Cadence 今(31 日)舉辦 Cadence LIVE Taiwan 2023 使用者年度大會,Cadence 資深副總裁暨數位與簽核事業群總經理滕晉慶在主題演講中指出,AI 晶片設計是下一波成長動能,不管 AI 伺服器、AI 基礎設施都需要台灣半導體供應鏈資源,是十年一遇的成長動能,能否以更智慧、更有效的方式分析新型態數據,是相當重要的問題。

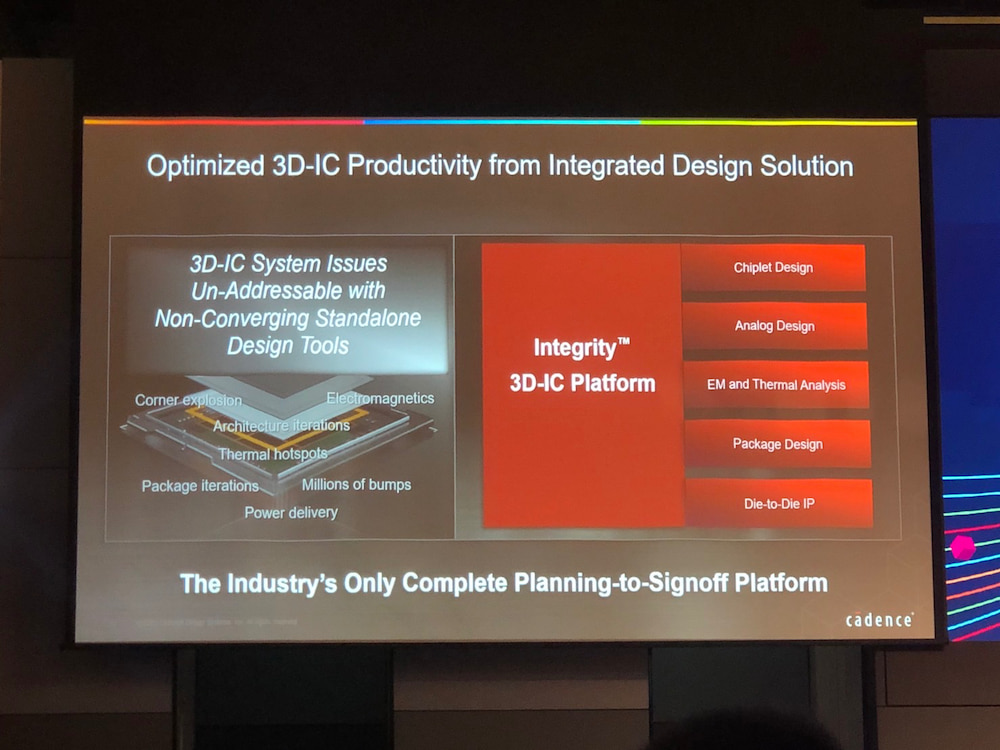

滕晉慶認為,目前看到許多客戶轉移三奈米以下製程,不管台積電、三星甚至日本政府都投資 3D IC 技術,也為目前產業帶來長期推動力。其中,熱管理是 3D IC 面臨的最大挑戰,熱管理、熱分析會變得非常重要,因此 Cadence 在 3D-IC 設計和封裝解決方案針對這個問題進行改善。

Cadence Integrity 3D-IC 平台為業界首個全面、高容量的 3D-IC 平台,可將設計規劃、實現和系統分析,整合在單個且統一的管理介面上;同時可支援 Cadence 的第三代 3D-IC 解決方案,通過熱完整性、功率和靜態時序分析能力,為客戶提供以系統級 PPA 表現,使之在單一小晶片(chiplets)中能妥善發揮效能。

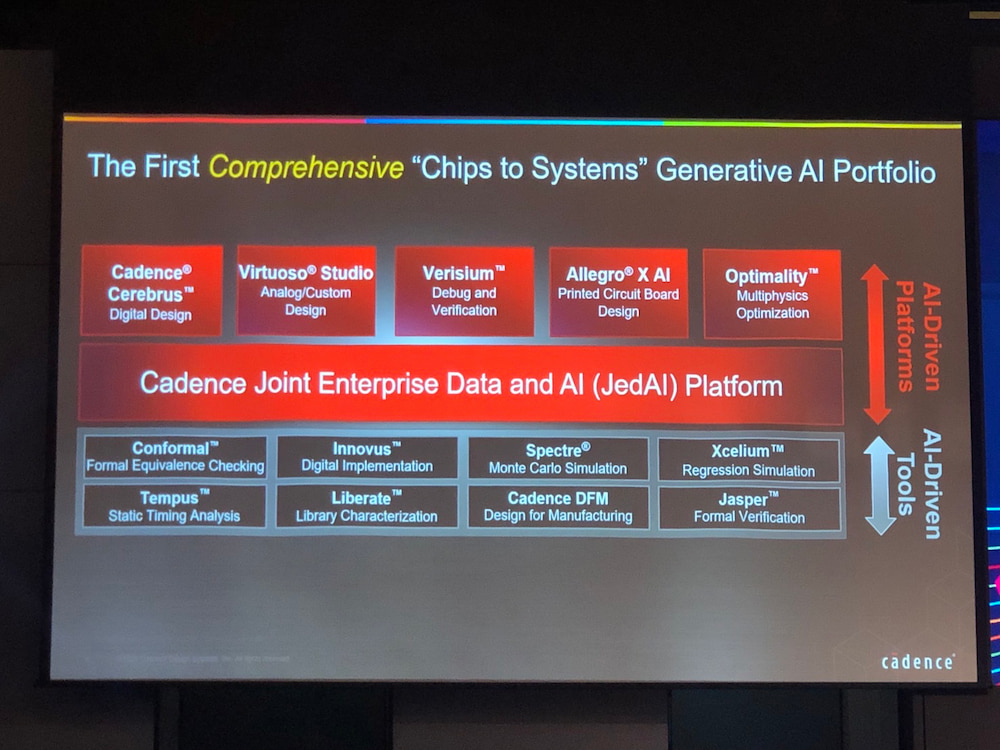

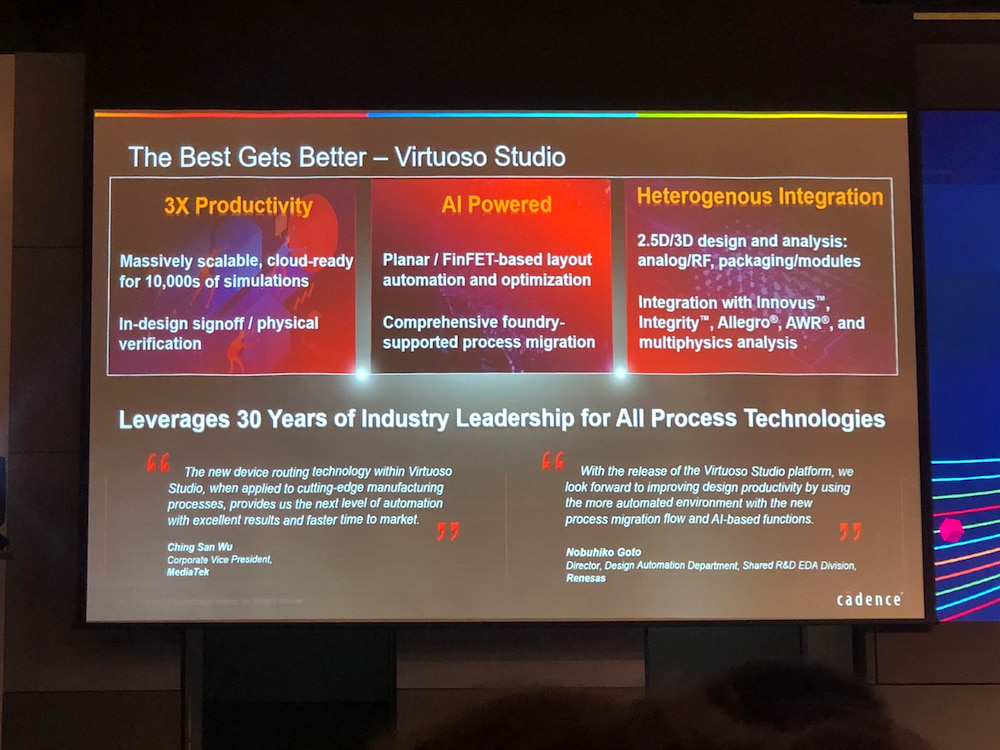

此外,Cadence 也嘗試透過 AI 技術來改善演算法,使其自動做出優化決策,減少工程師下決策的時間,因此推出結合 AI 技術的 EDA 工具與平台方案(JedAI),包括 Virtuoso Studio 和 Allegro X,並擁有晶片到系統各領域的工具,有效提供晶片生產力。

Cadence 表示,目前半導體業主要面臨三種挑戰,即晶片速度越來越快、功能越來越複雜、尺寸越來越大,但台灣整個產業鏈包括代工廠、封裝廠都有完整產業圈,可以獲得各個支援,在封裝擁有一定優勢。

因此,Cadence 已經在新竹成立研發中心,並在台投入研發投資,連結台灣半導體產業上下遊,掌握電子產品自主性及開發效率,推升台灣國際競爭力。

(首圖來源:科技新報)

延伸閱讀:

標題:AI 為十年一遇成長動能!Cadence AI EDA 工具、3D IC 方案克服挑戰小晶片、異質整合成半導體顯學!用最簡單的方式讀懂 Chiplet、SoC、SiP可摺疊螢幕促下波手機升級,台面板、鉸鏈供應鏈受惠

地址:https://www.utechfun.com/post/255629.html