來源:半導體行業觀察

英特爾試圖重回芯片制造和代工領域的前沿,而台積電定義這一前沿的舉措將在今年 12 月於舊金山舉行的國際電子設備會議 (IEDM) 上得到展示。

在一篇新聞中,台積電的研究人員表示,公司將在本屆的IEDM公布 N2 制造工藝,這是一種標稱 2nm 工藝,專爲 AI、移動和高性能計算而設計。在同一場會議的下一篇論文中,英特爾工程師將提供有關 RibbonFET(英特爾爲其納米片晶體管起的名字)的擴展細節。

在 IEDM 會議上,台積電的研究人員預計將報告稱,與 2022 年推出的 N3(標稱 3nm)工藝相比,N2 的速度可提高 15% 或功耗降低 30%,芯片密度也可提高 15% 或更高。

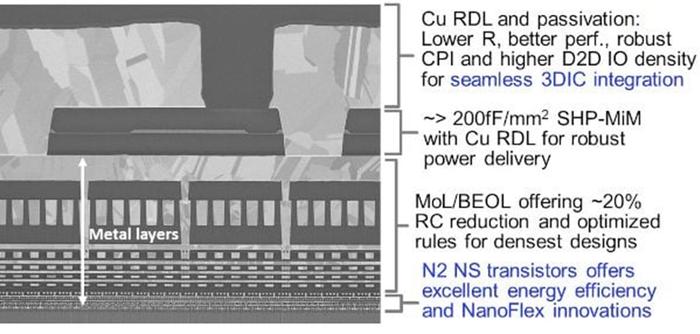

N2 互連堆棧的橫截面顯示銅重分布層。來源:IEDM 和 T 橫截面圖顯示,N2 平台的 Cu 重分布層 (RDL) 和鈍化層可與 3D 技術無縫集成。

台積電的 G. Yeap 等人撰寫的論文 2.1 2nm 平台技術,具有節能納米片晶體管和互連,與 3DIC 共同優化,適用於 AI、HPC 和移動 SoC 應用,還將展示具有世界紀錄密度爲每平方毫米 38Mbits 的 SRAM 宏。

本文還將詳細介紹中段(MEOL)和後端(BEOL)互連,其特點是可擴展的銅基重分布層,可靈活放置輸入/輸出焊盤並降低阻擋電阻);平坦的鈍化層(用於提高可靠性);以及硅通孔或 TSV(用於連接不同層的設備)。

研究人員表示,N2 平台已滿足晶圓級可靠性要求和初步資格測試。預計 2025 年實現全面認證,2026 年實現量產。

英特爾

在論文 2.2《6nm 柵極長度的硅 RibbonFET CMOS》中,來自英特爾的 A. Agrawal 等人准備展示如何構建具有 6nm 柵極和 45nm 接觸多晶硅間距(CPP,晶體管柵極之間的間距)的納米片技術 (RibbonFET),並且不會降低電子遷移率。

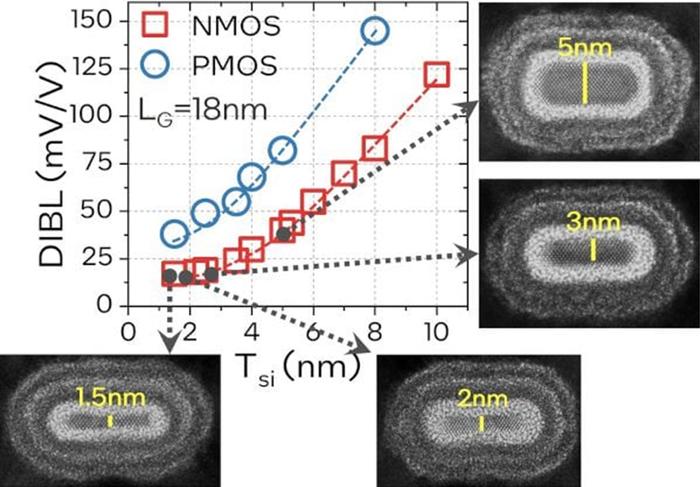

柵極長度爲 18nm 時漏極誘導勢壘降低 (DIBL) 與硅厚度 (Tsi) 的關系。隨着 Tsi 從 10nm 縮小到 1.5nm,DIBL 降低;然而,DIBL 降低在 Tsi

作者沒有提及英特爾的具體制造工藝,但 RibbonFET 計劃在 20A 工藝(即標稱 20 埃或 2nm 工藝)中投入生產。英特爾似乎選擇不推出任何基於 20A 的處理器產品,而是直接從 3nm 工藝轉向 18A 工藝,這可能反映在作者對納米片縮放的關注上。

研究人員將證明,在納米片硅厚度達到 3nm 之前,電子遷移率不會降低。此後,由於表面粗糙度而導致的電子散射成爲一個問題。在論文中,作者報告了 4nm 以下硅厚度的短通道控制和功函數工程如何實現以 3nm 爲基准的低閾值電壓。

2nm 技術競賽

英特爾、三星和台積電正處於在其 2 納米節點中實施背面供電技術的競爭前沿,旨在增強其在 AI 芯片市場的競爭力。這項創新技術有望通過將供電網絡重新定位到硅片背面來提高芯片效率,此舉旨在簡化電源效率、減少幹擾並提高整體性能。英特爾今年在商業化方面處於領先地位,三星電子和台積電緊隨其後,准備在 2025 年進行大規模生產,業界對背面供電的變革性影響充滿期待。

工程師在縮小半導體芯片上晶體管的尺寸時面臨哪些挑战,背面供電技術的採用將如何重塑半導體制造和設計的格局,以及這一進步將如何影響未來移動應用處理器和人工智能芯片的發展?

一、要了解的關鍵事項:

英特爾引領潮流:英特爾將於今年利用其 PowerVia 解決方案將背面供電技術商業化,旨在提高芯片性能和效率。

競爭優勢:背面供電技術提高了電源效率並減少了幹擾,這對人工智能應用和移動處理器至關重要。

行業轉變:三星和台積電也在迅速推進其背面供電技術,三星的目標是到 2025 年實現大規模生產。

重大影響:背面供電技術的採用有望改變半導體制造工藝,實現更緊湊、更高效的芯片設計,並推動整個行業的創新。

二、微型化的極限:未來設備進步的瓶頸

對微型化的不懈追求一直是電子技術進步的驅動力,使更小、更強大、更節能的設備得以誕生。然而, 隨着工程師們 接近晶體管尺寸的根本極限,晶體管縮小所帶來的挑战开始阻礙進一步的微型化。幹擾增加、功率效率降低以及芯片正面電路和電源线空間有限,這些因素共同阻礙了 更先進設備的开發 ,引發了人們對設備微型化未來的擔憂。

三、小型化中的技術挑战

隨着晶體管變得越來越小,工程師面臨着衆多技術挑战,如果不加以解決,可能會對電子設備的性能和可擴展性產生連鎖反應。材料的物理限制和 物理原理(如量子隧穿和散熱)給半導體芯片的設計和制造帶來了重大障礙。芯片正面電路和電源线的擁擠加劇了這些問題,導致電力輸送效率降低,信號傳輸幹擾增加。

傳統的前端供電方法一直是業界的標准做法,但這種方法根本無法適應現代電子設備的復雜性。芯片前端的電源线和數據傳輸路徑非常接近,這會導致串擾、噪聲和信號幹擾,從而降低電子元件的性能並增加能耗。空間的縮小還會導致發熱量增加,進一步影響供電效率和 設備的整體功能。

四、設計限制和集成問題

此外,半導體芯片正面設計的限制阻礙了附加電路和電源线的集成,從而限制了電子設備的功能。隨着芯片上晶體管密度的增加,安裝緩衝器、驅動器和控制電路等額外組件成爲一項挑战,限制了 設備的整體設計靈活性和功能性。空間的減少也降低了提高功率效率的潛力,阻礙了低能耗電子系統的开發, 而這些系統對於未來電子設備至關重要,因爲它們要努力滿足日益嚴格的能源和碳排放標准。

五、英特爾的背面供電:半導體行業的遊戲規則改變者

追求更小的芯片尺寸和更高的功率效率已成爲行業巨頭英特爾、三星和台積電之間競爭的關鍵因素。背面供電技術(將供電網絡從硅片正面移至背面)的實施是這場競爭的核心,三家公司都在競相率先將這一創新解決方案商業化。

六、背面供電面臨的挑战

實現高效背面供電面臨的主要挑战之一是在芯片的有限空間內集成電源和信號布线。根據英特爾最近的 PowerVia 測試,將供電與信號路徑分離可顯著提高單元利用率,實現 90% 以上的效率。這對於滿足日益增長的 AI 和圖形應用需求至關重要,因爲這些應用需要高密度和高性能的芯片設計。

背面供電的優勢非常顯著,它不僅能提高芯片性能,還能提高電源效率並減少信號幹擾。借助這項技術,芯片可以變得更小,這對於需要低能耗和緊湊設計的移動應用處理器來說是一個很大的優勢。使用 背面供電還可以減少對配電層的需求,從而減少制造步驟總數並降低與半導體生產相關的成本。

六、解決互連瓶頸

英特爾的創新方法(如其 PowerVia 技術所示)還解決了互連瓶頸問題。通過將電源布线移至晶圓背面,英特爾解決了芯片設計中最緊迫的挑战之一。這不僅簡化了制造過程,還改善了熱管理,這對於保持高密度電路的性能和可靠性至關重要。

雖然英特爾有望憑借其 PowerVia 解決方案率先實現背面供電商業化,但三星和台積電正在迅速崛起。三星將其商業化時間表從最初計劃的 2027 年提前到 2025 年,這表明該公司在背面供電技術方面的發展速度很快。有報道稱,三星可能會從 1.7nm 工藝开始實施這項技術,2nm 工藝將是主要重點。然而,台積電一直對其計劃保持沉默,對其开發進度保密。

七、PowerVia 增強性能

英特爾在 PowerVia 方面的進步不僅限於電源效率。採用 PowerVia 技術的測試芯片顯示平台電壓下降改善了 30%,頻率性能提高了 6%。這些增強對於 AI 芯片的整體性能具有重要意義,因爲它們確保了穩定高效的電力輸送,這對於高性能計算任務至關重要。

英特爾在這一領域的發展尤其值得關注,即將推出的 Arrow Lake 台式機 CPU 將採用 英特爾 20A 節點和 PowerVia 技術。該公司計劃在今年晚些時候推出首款 2nm 芯片, 這進一步 表明了其對這項創新技術的承諾。英特爾 20A 節點使用背面供電 不僅可以提高芯片性能,還可以 提高電源效率,這是業界追求降低能耗的關鍵因素。

此外,英特爾專注於將 PowerVia 开發與晶體管進步分離开來,這使得他們能夠獨立完善這項技術。這一策略確保在將 PowerVia 與英特爾的下一代 RibbonFET 晶體管(將在 20A 工藝節點中引入)集成之前對其進行優化。這種有條不紊的方法有助於降低風險並確保無縫過渡到更先進的半導體節點。

八、解耦 PowerVia 开發

英特爾、三星和台積電之間的競爭愈演愈烈,每家公司都在努力實現更小的芯片尺寸和更高的功率效率。背面供電技術的實施 是這場競爭中的重要一步,因爲它可以提高芯片性能、提高功率效率並減少信號幹擾。雖然英特爾將首先實現這項技術的商業化,但三星和台積電正在迅速崛起,三星正在推進其商業化時間表,而台積電則對其开發進度保密。縮小尺寸的競爭 仍在繼續,背面供電技術的推出標志着半導體制造的新時代。

九、背面供電改變半導體制造

半導體行業正處於十字路口,隨着英特爾、三星和台積電等芯片制造商 將重點轉向 提高 2nm 技術節點的功率效率和減少幹擾,背面供電技術的採用勢頭強勁。這種從傳統正面供電系統的轉變是爲了應對電路設計尺寸縮小帶來的日益嚴峻的挑战,其結果可能會改變 AI 芯片市場以及未來移動應用處理器 (AP) 和 AI 芯片的發展。

十、IEEE 認可和英特爾的領導地位

IEEE 已將背面供電確定爲下一代 2nm 工藝節點的關鍵技術,該技術有望通過提高電源效率和性能來提供競爭優勢,而這對 AI 應用至關重要。憑借其 PowerVia 技術,英特爾有望引領潮流,旨在將其集成到即將推出的 20A 節點和 Arrow Lake CPU 中。高效供電的能力將爲行業樹立新標准,爲提高 AI 芯片的性能和效率鋪平道路。

背面供電對未來移動 AP 和 AI 芯片的發展影響 巨大,該技術可實現更緊湊、更高效的設計。通過縮小芯片尺寸,背面供電可顯著造福移動設備,實現更先進的 AI 應用,同時提高功率和頻率效率。該技術還有望減少信號幹擾和制造挑战,從而爲整個行業帶來更強大、更可靠的 AI 應用。

十一、芯片架構的創新與小型化

採用背面供電技術爲芯片架構和制造工藝的創新开闢了新途徑,爲半導體技術的進一步小型化和效率提升奠定了基礎。領先的芯片制造商盡早採用和改進這項技術可能會加速整個 半導體行業的進步,從而开啓半導體制造的新時代。

半導體行業 處於技術創新的前沿,向背面供電技術的轉變是提高電源效率、減少幹擾和推動半導體制造進一步進步的重要一步。隨着英特爾、三星和台積電等芯片制造商繼續在這一領域取得進展,業界有望 看到 緊湊高效的設計、人工智能應用性能的提升,以及芯片架構和制造工藝創新的新機會。

參考鏈接

https://www.eenewseurope.com/en/intel-tsmc-to-detail-2nm-processes-at-iedm/

標題:2nm,即將公布

地址:https://www.utechfun.com/post/430177.html