3nm量產還沒多久,2nm就已經被各大廠商提上了日程。

台積電在2023年報裏指出,台積電的2nm研發着重於基礎制程制定、良率精進、電晶體及導线效能改善以及可靠性評估,預計2024年內,重要客戶完成芯片設計,並开始做驗證。

英特爾是副總裁在採訪中表示,英特爾的20A即2nm工藝將在2024年進入量產,而英特爾准備再次引領小型化,其中Arrow Lake是主導產品,預計將於2024年下半年推出。

三星呢,則是在財報中表示,其代工廠將在6月正式推出SF2即2nm工藝,SF2的PDK、EDA 工具和授權 IP)將在2024年第二季度完成,隨後合作夥伴就能使用SF2來設計制造芯片。

三大代工廠都把2nm的推出當成是一場重頭戲,但目前我們仍然心存疑問:2nm到底能用來幹什么?它能在多大程度上改變目前的芯片?

最近,台積電執行副總裁兼聯席首席運營官米玉傑與AMD首席技術官馬克·佩珀馬斯特 (Mark Papermaster)展开了有關於2nm的對話,這或許能幫助我們對2nm以及之後的世界有一個更深入的理解。

物理和創新的界限

在這次談話中,台積電首席運營官米玉傑首先提到了2nm的艱難,台積電從0.5微米开始到2nm,在三十余年的時間裏,晶體管的縮放超過了4000倍,但隨着制程的升級,擴展也變得越來越有挑战性,但他認爲,2nm之後仍然有發展空間,成功關鍵就是客戶合作。

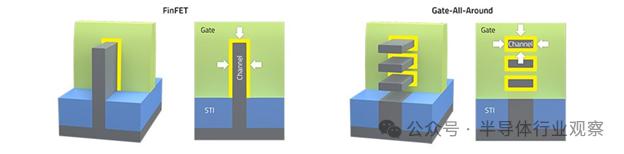

米玉傑表示,先進制成的進化還未停止,機會和挑战機會並存,台積電採用雙研發團隊體制,通過兩支團隊交替推出最新制程,擁有更多時間和技術資源,雖然目前每代制程开發周期長達五年甚至七年,較之前二至三年明顯放緩,但未停止。他強調,7nm制程之後,台積電每一個新制程都會導入新技術,2nm將導入更復雜的GAAFET技術,暫定2025 年量產。

他也提到,台積電正在开發技術,包括硅光子技術、與 DRAM 供應商合作來優化HBM,以及研究將n和p兩種MOS器件相互堆疊在一起的CFET晶體管方案等。台積電未來還會進行更多开發,以推動半導體業繼續向前。

而AMD的首席技術官佩珀馬斯特也對目前先進制程提出了自己的看法,他表示,2010 年代初以來,傳統代工廠和無晶圓廠IC 設計企業合作模式逐漸顯露不足,在現在的代工市場中,甲乙方需要達成更密切的合作,大家一同努力來讓芯片發揮應有的性能。

佩珀馬斯特認爲,台積電所強調的設計制程協同最佳化(DTCO,Design-Technology Co-Optimization)作用越來越大。一方面DTCO 有助辨識過於極端而缺乏價值的制程路线,聚焦客戶真實需求,減少开發壓力,另一方面,DTCO 可幫助客戶產品性能、能耗、芯片面積三大要素間取得平衡,達成單純制程微縮難實現的目標。DTCO 也有助發揮單一節點的技術潛力。

佩珀馬斯特所提到的DTCO,可能有很多人對它還不夠了解,這項神祕方法,在台積電在過去幾個世代先進制程的效能提升方面扮演了重要角色。

DTCO即設計技術協同優化,如其字面所示,就是設計與制程技術尋求整合式的優化,來改善效能、功耗效率、電晶體密度、以及成本,台積電此前曾表示,制程研發團隊與設計研發團隊一开始就必須攜手合作,針對下一世代技術的定義進行設計技術協同優化,兩個團隊必須保持开放的心態,探索設計創新與制程能力的可能性,許多創新的想法都在這個階段被提出來,其中有些想法可能太積極而無法借由既有技術實現,有些想法初步看起來可能很有潛力,但是結果卻沒那么實用,而設計技術協同優化的目的就在於定義真正有意義的調整,超越單純的幾何微縮,進而達成提升效能、功耗、面積的目標。

舉例來說,台積電的7nm就是設計技術協同優化成功的證明之一。其在16nm率先採用鰭式場效(FinFET)晶體管結構時,採用三鰭結構於單一標准元件,提供優於平面式電晶體的驅動強度。基於鰭式分離的特性,第一代FinFET技術使用通用型鰭式柵格(global fin grid)將鰭的置放彈性最大化,此類型柵格預先設定好鰭的放置位置,是一種應用在整個芯片上支持邏輯及混合新號設計的通用鰭式柵格系統。

邁入到7nm時,台積電發現通用型鰭式柵格也許不是優化效能、功耗、面積的最佳選擇,因此在進行設計技術協同優化探索時推出特殊型鰭式柵格(local fin grid)的概念,創造了優化標准元件鰭片置放的靈活性,並將寄生電容和電阻降到最低。如此一來,相較於前一世代制程,我們能夠使用更少的鰭數量來達到所需的效能,同時提升密度。相較於10nm制程,DTCO讓台積電的7nm制程邏輯密度增加超過1.6倍,速度增快約20%,功耗降低約40%。

DTCO從整體角度審視設備如何相互交互以及它們如何同時滿足多種要求,並促使代工廠尋找構建設備的新方法,它成爲了從平面晶體管過渡到 finFET 晶體管的關鍵因素,而從 finFET 中汲取的工程經驗成爲了全柵納米片晶體管以及未來叉片晶體管和 CFET 的推動者。

當傳統的擴展方法开始力不從心時,DTCO 才真正开始受到重視。通過共同優化設計與技術、系統與技術,系統架構師可以從技術中獲得比傳統擴展方法更多的優勢,孤立的設計和工藝步驟需要發展成爲跨職能團隊,廣泛的合作已被認爲是推動半導體發展的關鍵,伴隨着GAA的推出,DTCO的重要性愈發凸顯。

佩珀馬斯特作爲芯片設計公司的技術人員,與來自晶圓代工廠的米玉傑在這一方面達成了共識:2nm乃至更先進的制程,不再是晶圓代工廠的閉門造車,而是需要更多設計公司的助力,伴隨制程的不斷推進,代工廠和設計公司也結合得愈發緊密,多方合作來延續摩爾定律。

來自Chiplet的助力

對於2nm之後的芯片技術,AMD也在另一段視頻中提出了新的觀點,AMD首席技術官佩珀馬斯特與AMD 高級副總裁兼企業研究員薩姆·納夫齊格(Sam Naffziger)討論了Chiplet,如何將半導體分解成以新穎的方式組裝在一起的組件,並以此挑战摩爾定律的放緩,或許也可以爲2nm乃至之後的半導體業界提供助力。

佩珀馬斯特和納夫齊格都強調了芯片標准化的重要性。

“特定領域的加速器,是實現每瓦每美元最佳性能的最佳途徑。因此,這對於取得進步絕對是至關重要的,”納夫齊格解釋說,“你不可能爲每一個領域都提供特定的產品,所以我們能做的是建立一個芯片生態系統——本質上是一個庫。”

納夫齊格指的是通用芯片組互連 Express(UCIe)——一種芯片組通信的开放標准,該標准自 2022 年初創立以來,已經贏得了包括 AMD、ARM、英特爾和英偉達在內的巨頭廣泛支持,不少中小型企業也在嘗試接入這一標准。

AMD 自 2017 年推出第一代 Ryzen 和 Epyc 處理器以來,一直走在芯片組架構的前沿。如今,Zen的芯片庫已經發展到包括多個計算、I/O 和圖形芯片,並將其組合打包到消費級和數據中心處理器中。而AMD 於 2023 年 12 月推出的 Instinct MI300A APU 就是芯片組的實例之一,它包含 13 個獨立的芯片——4 個 I/O 芯片、6 個 GPU 芯片和 3 個 CPU 芯片,以及 8 組 HBM3 內存。

納夫齊格表示,在未來,像UCIe這樣的標准可能會讓第三方制造的芯片組進入AMD的封裝中,他提到了硅光子互連,這種可以緩解帶寬瓶頸的技術,在未來有可能將第三方芯片帶入 AMD 產品。不過他也認爲,如果沒有低功耗的芯片到芯片互連技術,硅光子互連是不可行的。

納夫齊格說:“你將光學技術安裝在芯片上,是因爲你需要巨大的帶寬。因此你需要每比特的相對低能耗,這樣才有意義,而封裝內芯片是獲得低能耗接口的途徑。"他認爲向共同封裝光學技術的轉變“即將到來”。

爲此,幾家硅光子初創公司已經在推出這樣的產品。例如,Ayar 實驗室开發了一種兼容 UCIe 的光子芯片組,該芯片組已集成到英特爾去年制造的圖形分析加速器原型中,不過截至目前,第三方芯片(無論是光子芯片還是其他芯片)還沒有正式進入到 AMD 產品中,有待進一步的發展,要實現異構多芯片,標准化只是需要克服的衆多挑战之一。

值得一提的是,AMD 曾經向競爭對手的芯片制造商提供過芯片組,英特爾在 2017 年推出的 Kaby Lake-G 部件採用了 Chipzilla 的第八代內核和 AMD 的 RX Vega GPU,該部件最近又出現在 Topton 的 NAS 板上。

納夫齊格此前還接受過IEEE Spectrum的採訪,在關於Chiplet如何改變半導體制造工藝這一問題上,他也發表了自己的看法。

“這絕對是該行業正在努力解決的問題。這就是我們今天所處的位置,也是我們 5 到 10 年後可能發展的方向。我認爲現在的技術基本上都是通用型的,它們可以很好地與單片芯片相匹配,也可以用於芯片組。對於芯片,我們擁有更專業的知識產權。因此,我們可以設想在未來實現工藝技術的專業化,並獲得性能優勢、成本降低和其他方面的好處。但這並不是目前的產業現狀。” 納夫齊格說到。

納夫齊格表示,AMD架構的目標之一是讓它對軟件完全透明,目前AMD正在想方設法擴展邏輯功能,但 SRAM 是一個更大的挑战,而模擬功能肯定無法擴展。AMD已經採取了將模擬與中央 I/O 芯片分離的措施,如3D V-Cache——一種與計算芯片三維集成的高密度緩存芯片,他希望未來會有更多這樣的專用化產品。

在摩爾定律放緩的如今,Chiplet能幫助AMD實現更多技術上的愿景,即便是制程推進至2nm之後,Chiplet也能幫助解決SRAM這樣的痛點,截至目前,標准化是Chiplet亟需解決的一個問題。

寫在最後

2nm的爭奪战目前已經悄然展开,台積電、英特爾和三星开始尋找自己的客戶,數以百億計的美元砸向了新的晶圓廠,第一個大規模量產2nm芯片的廠商,無疑會引領之後的工藝制程革命。

但對於AMD這樣的無晶圓廠公司來說,2nm這樣的昂貴的先進制程,不是單純的提升芯片的晶體管密度,還要顧及未來的架構演進,以及先進封裝等技術的交匯融合,如何權衡2nm乃至1.6nm的工藝,又給未來的芯片設計行業提出了新難題。

標題:2nm,芯片巨頭怎么看?

地址:https://www.utechfun.com/post/372299.html