在 IMEC (比利時微電子研究中心) 舉辦的 ITF World 2024 大會上,AMD 董事長兼執行長蘇姿豐領取了 IMEC 創新大獎,表彰其行業創新與領導。此前英特爾創辦人的 Gordon Moore、微軟創辦人比爾·蓋茨 Bill Gates、台積電創辦人張忠謀也都得到過這個榮譽。

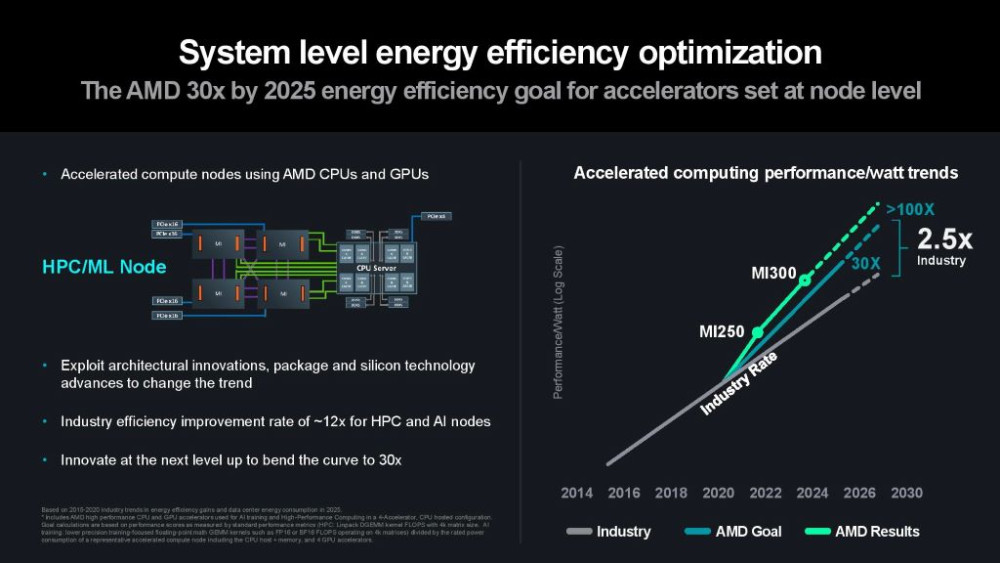

在獲獎後的演講中,蘇姿豐談到,AMD 正在全力衝刺 30×25 的目標,也就是到 2025 年將計算能效提升到 2014 年的 30 倍,而到了 2026~2027 年,AMD 計畫進一步把計算能效提升到 2014 年的 100 倍。這一速度,將遠超業界平均水準。

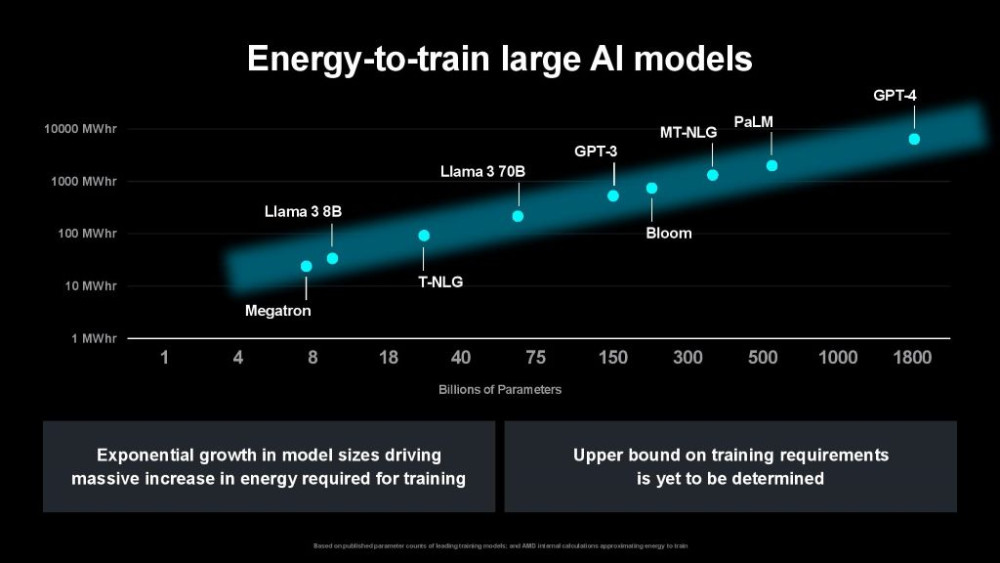

隨著處理器、顯示卡等處理器的能耗越來越高,AMD 早在 2014 年就設定了名為 25×20 的目標,也就是到 2020 年將產品能效提升 25 倍,最終超額做到了 31.7 倍。隨後,AMD 又立下了 30×25 的新目標,預計 2025 年就能順利實現。蘇姿豐對此指出,眼下提升運算產品能效的最大障礙就是 AI 大模型訓練、微調所需的龐大算力。因為這往往離不開成千上萬的 GPU,以及成千上萬兆瓦的電力,而且當前還在急劇成長當中。

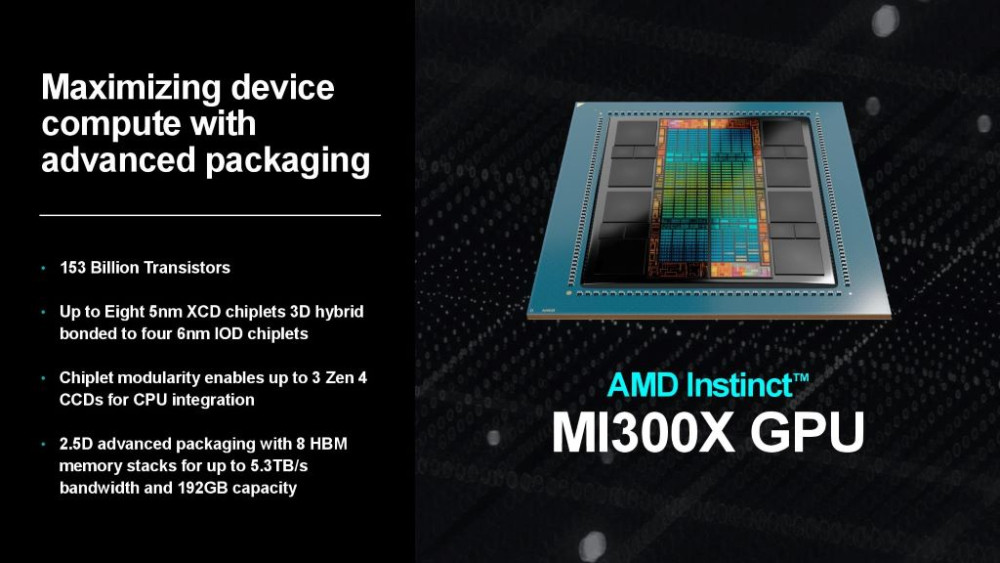

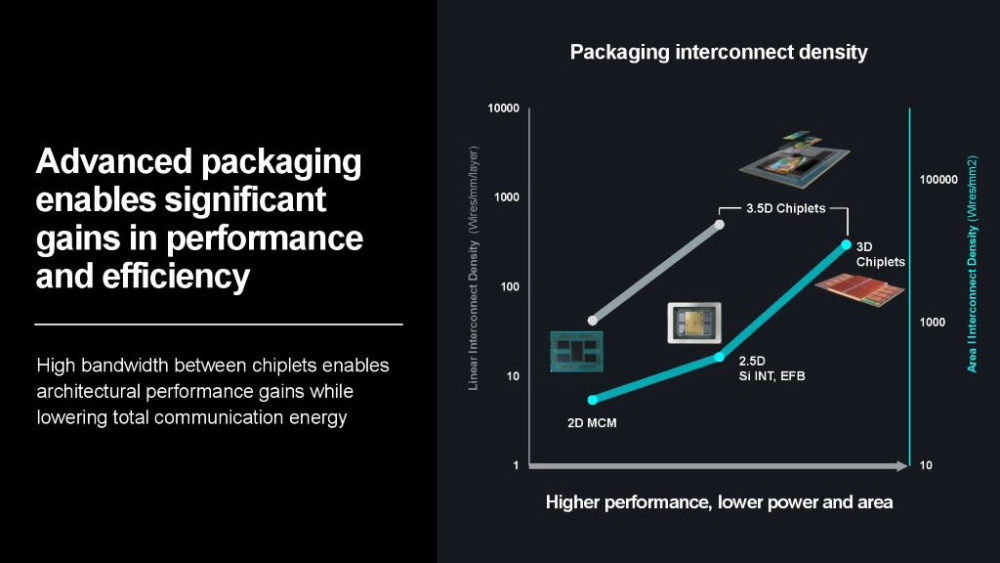

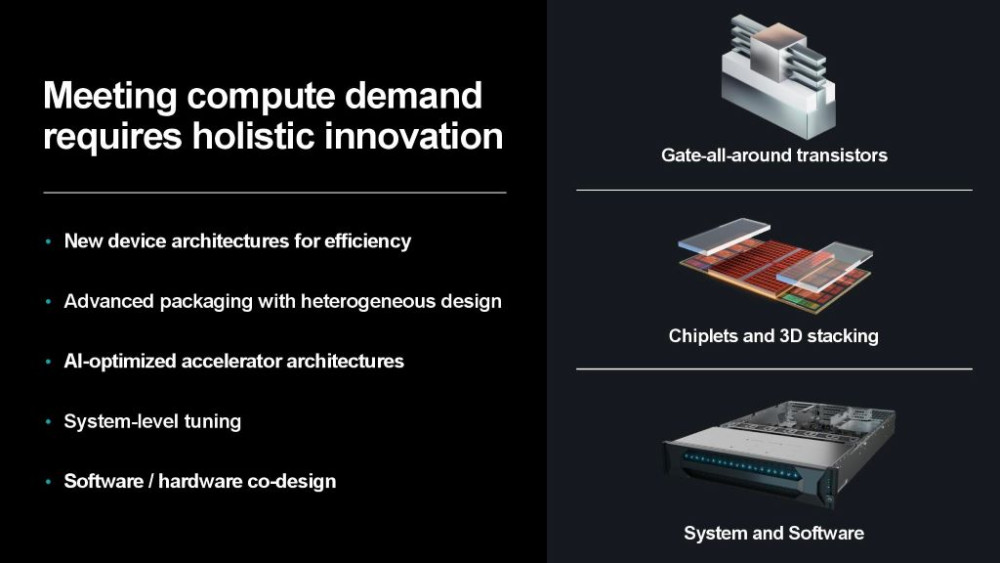

為此,AMD 將多管齊下,從產品架構、製程技術、封裝技術、互連技術等方面提升能效,比如 3 奈米 GAA 全環繞柵極製程技術,以及 2.5D/3D 先進封裝技術等等。蘇姿豐強調,AMD 最強的 AI 晶片 Instinct MI300X 就是高能效的典型代表,其擁有 1,530 億個電晶體,分為 12 顆小晶片,還整合了 24 顆共 192GB HBM3 記憶體。

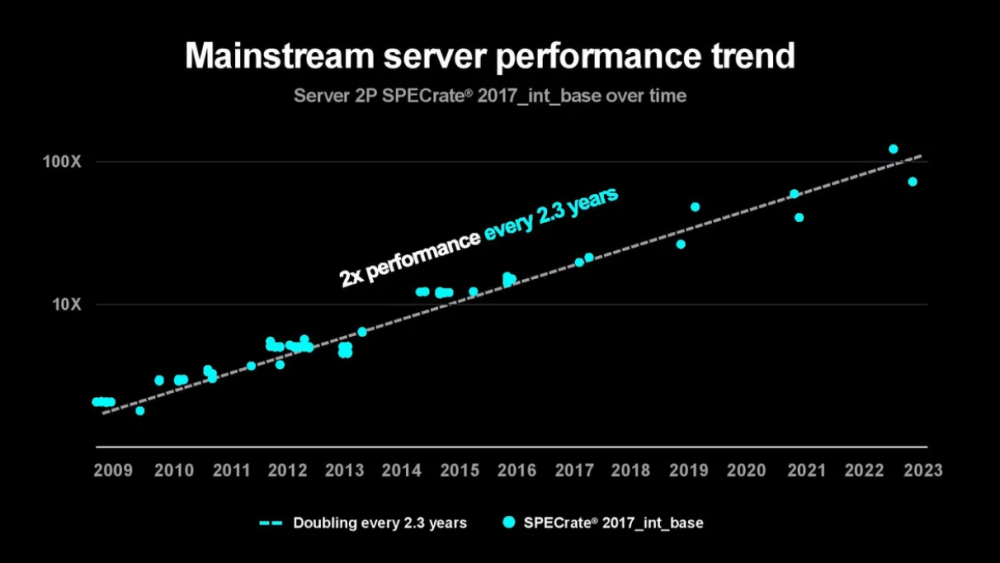

另外,核心執行序數量從單核心/單執行序,增加到 96 核心/192 執行序,頻率從 20MHz 提高到 3.5GHz,暫存記憶體容量從 16MB 增加到 486MB,內核心面積從 49 mm² 增加到 1240mm² 所有這些技術都可以作為 GPU 使用,透過與封裝內單元之間的功率和性能優化,加上無限結構互連相結合,使運算和記憶體密度能更接近處理核心,從而減少傳輸數據所需的能量。

蘇姿豐進一步強調,雖然硬體優化很重要,但 AMD 在軟硬體協同優化方面的工作也取得了令人矚目的成果。使用較低精度的數位格式可以提高能源效率和能耗,使得特定硬體加速的設計對於持續擴展變得非常重要。尤其,轉向 FP4 等較低精度格式,相較於FP32 會大幅增加每焦耳消耗能量,包括對 FP8 的能耗提高了 15 倍,而 FP4 的能耗則是提高了約 30 倍。

不過,因為較低的精度會導致較低的準確度。對此,蘇姿豐強調,先進的量化技術有助於解決這個問題。事實上,即使 MXFP6 也能產生與 FP32 相似的精度,只有少數不同模型的 MXFP4 上出現了下降,而其他模型仍然同樣準確。當前,提高低精度格式準確性的工作仍在繼續,因此 AMD 甚至可以看到 MXFP4 在未來的更多模型中變得與 FP32 一樣準確。

蘇資豐最後指出,總體而言,AMD 在每個節點的電源效率方面已經超過了業界的進步速度,而該公司還在努力實現 30 倍的電源效率提高。預估這種趨勢將持續下去,而且透過這種類型的創新,將依照我們今天所看到的情況,預計 AMD 可以做得更好。到 2026 年和 2027 年,我們有望實現超過 100 倍的目標。

(首圖來源:AMD 提供)

標題:AMD 將晶片運算效能提升百倍,蘇姿豐:2026~2027 年達成

地址:https://www.utechfun.com/post/375582.html