導讀 外媒報導,如果現在業界渴望利用單一晶片獲得更多的功能,製程微縮將不再是唯一方法,而是採多個小晶片相互連接以提升性能,成為主流。人工智慧和高效能運算大幅成長時代,運算能力比以往更重要,使先進封裝引領產...

外媒報導,如果現在業界渴望利用單一晶片獲得更多的功能,製程微縮將不再是唯一方法,而是採多個小晶片相互連接以提升性能,成為主流。人工智慧和高效能運算大幅成長時代,運算能力比以往更重要,使先進封裝引領產業前進發揮至關重要的作用,且還會持續。

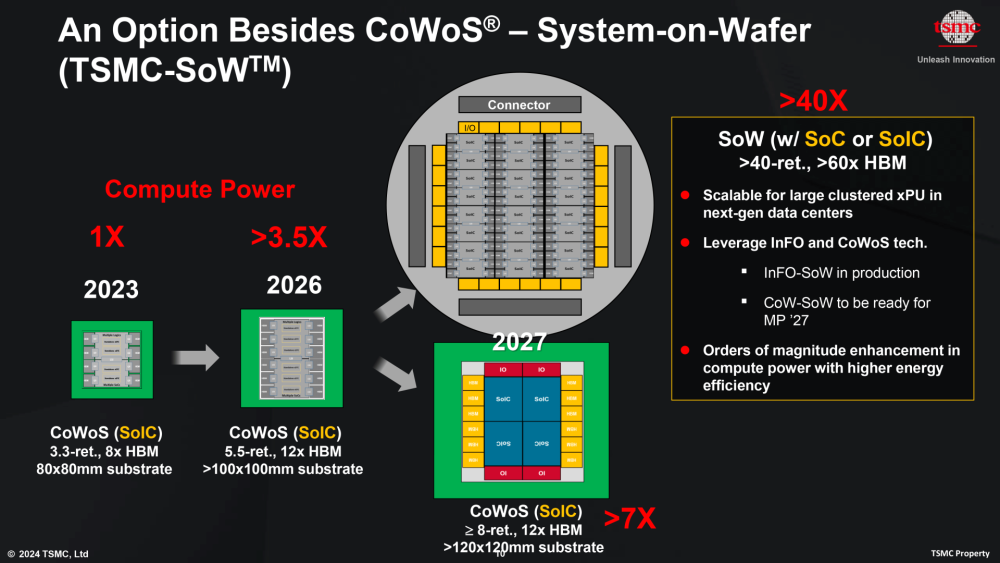

Wccftech 報導,台積電技術研討會展示 A16 先進製程,透露許多細節,CoWoS 封裝允許達台積電光罩尺寸 3.3 倍,光罩尺寸是指標準尺寸限制乘數,以確定有效的可用面積,簡單來說就是乘數越大越好。

滿足未來需求後,台積電透露 2026 年推出 CoWoS-L 先進封裝,採光罩尺寸達 5.5 倍,這代表可用 12 個 HBM 記憶體堆疊,容納更大基板,尺寸達 100×100mm。台積電生產晶片運算效能將提高到上代 3.5 倍,還只是開始,因台積電有更大計劃。

台積電 2027 年推出八倍光罩尺寸 CoWoS 先進封裝,支援更大 120×120mm 基板,整合四種 SoIC,為市場樹立新技術門檻。台積電還提到專用 SoW 封裝標準,有 40 倍光罩限制及可用 60 個 HBM 堆疊,滿足資料中心運算需求。台積電還將達成 40 倍光罩,對半導體產業是很重要的事。

整體來說,先進封裝進步代表製程微縮不再是決定運算力的唯一途徑,CoWoS 將在塑造人工智慧和高效能運算產業,扮演關鍵角色。

(首圖來源:科技新報攝)

關鍵字: , , , ,

標題:台積電以更大光罩,滿足先進封裝運算需求

地址:https://www.utechfun.com/post/365752.html