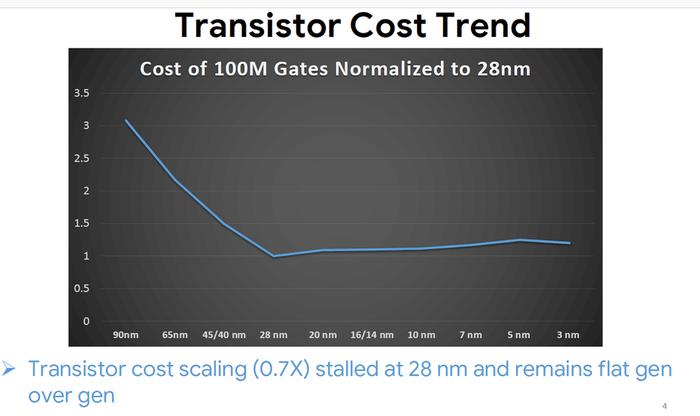

IT之家 2 月 4 日消息,芯片行業一直遵循着摩爾定律,即每兩年集成電路上的晶體管數量翻一番,成本減半。然而,這一定律似乎正在失去效力。MonolithIC 3D 公司首席執行官 Zvi Or-Bach 在 2014 年就提出,28 納米制程以後,晶體管的單位成本已經停止下降。近日,谷歌的 Milind Shah 也證實了這一觀點,他的研究表明,自 2012 年台積電量產 28 納米平面工藝以來,1 億門晶體管的單位成本實際上有所上升。

圖源:台積電

圖源:台積電

谷歌的研究結果顯示,“晶體管成本下降在 28 納米時停滯,並且代際變化持平。”

多年來,業界對於新制程節點晶體管單位成本的遞減收益一直持擔憂態度。最新的芯片制造工藝,例如 7nm、5nm 和 3nm,需要更復雜昂貴的制造設備,成本動輒數億美元。例如,一台 ASML Twinscan NXE 光刻機就需要 2 億美元。這將尖端晶圓廠的建設成本推高至 200 億至 300 億美元,導致芯片生產成本居高不下。

IT之家注意到,Milind Shah 在 IEDM 行業展會上展示的圖表顯示,以 28 納米爲基准的 1 億門晶體管成本實際上持平甚至有所上升,這種成本停滯使得部分芯片設計不愿採用最新制程。相反,將芯片分解成多個小芯片(chiplet)並進行集成變得更具吸引力。例如,AMD 的 Ryzen 桌面 CPU 和英特爾的 Meteor Lake 筆記本 CPU 都採用了這種方式,由 3 到 4 個採用不同制程的芯片組成。

然而,多芯片設計也存在一些挑战。首先,它們通常比單芯片設計更耗電,不適合移動設備。其次,多芯片集成是一項復雜的工程任務,雖然像 MonolithIC 3D 這樣的公司提供集成服務,但其成本不菲。最後,先進封裝技術本身也昂貴,而且獲得封裝產能的難度與先進制程不相上下。

雖然新制程不再能降低晶體管成本,但對於無法有效分解或分解難度較大的芯片設計來說,它們仍然具有重要意義。

標題:芯片制造成本瓶頸浮現,十年前價格就已停止下降

地址:https://www.utechfun.com/post/327848.html