陽明交大光電工程系講座教授劉柏村率領團隊與美國德州農工大學教授、玉山學者郭育進行國際合作研究,結合材料、元件、電路三個不同的面向,開發可應用在單晶片三維積體電路的互補型場效電晶體技術(Complementary Field Effect Transistor,CFET),研發成果具有下世代埃米級(Angstrom)積體電路技術應用的極高價值。

隨著半導體技術與產業的快速發展,為打破元件物理尺度微縮上的限制並持續遵循摩爾定律發展軌跡,單晶片三維積體電路(Monolithic Three-dimensional Integrated Circuits,M3D-ICs)的概念被提出。

所謂 M3D-IC 技術是指電晶體的布局結構將朝向多層級垂直堆疊邁進,並在有限的面積下大幅提高電晶體元件數量的密度,未來有望能實現超越摩爾定律目標,以打造更快速且低成本的小型晶片,為進一步的製程微縮帶來希望,並獲國際知名學術期刊《尖端科學》(Advanced Science)刊登。

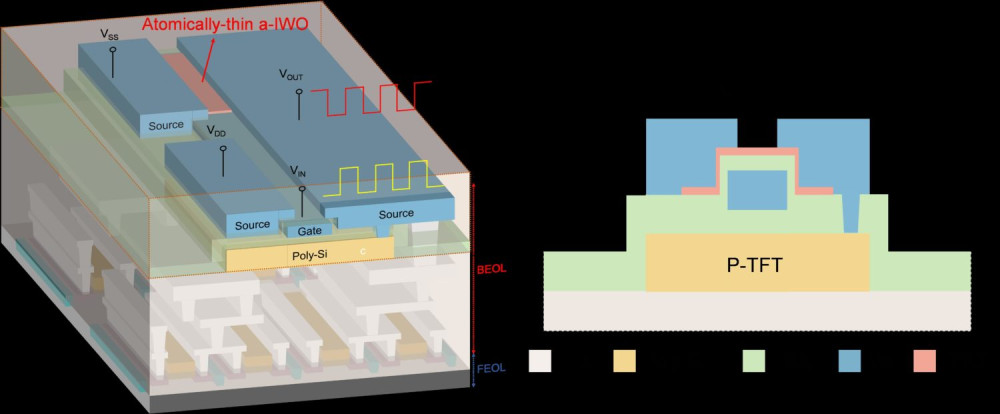

▲ 可應用於單晶片三維積體電路垂直堆疊互補式異質場效電晶體元件結構。(Source:陽明交大)

▲ 可應用於單晶片三維積體電路垂直堆疊互補式異質場效電晶體元件結構。(Source:陽明交大)

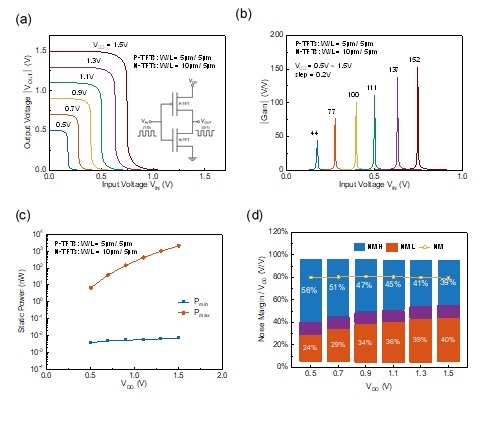

研究團隊採用新穎的氧化銦鎢(amorphous indium tungsten oxide,a-IWO)半導體材料,能在通道只有約幾層原子的厚度下展現優異的電流表現特性,並使邏輯電路成功達到高電壓增益(High Voltage Gain)、皮瓦特(Pico-watt)的極低靜態功耗,以及卓越且對稱的雜訊邊限(High Nosie Margin)等高效特性。

研究團隊用新穎的半導體材料及創新技術,克服單晶片三維積體電路技術的技術挑戰,這項研究成果特性可媲美目前半導體工業所使用的矽基元件,達到更優越的電性效能,並具有下世代埃米級積體電路技術應用的極高價值,實現超高電晶體密度異質晶片材料整合技術,能在較低的功率損耗下發揮高效能電晶體元件特性。

▲ 單晶片三維垂直堆疊互補式異質場效電晶體組成的反相器電路於不同操作偏壓下,達到(a)低操作偏壓的電壓轉換曲線(Transfer Characteristics),(b)高電壓增益(152V/V),(c)皮瓦(pW)等級的超低靜態功率耗損,(d)高對稱性雜訊邊限特性(~80%)的表現能力。(Source:陽明交大)

▲ 單晶片三維垂直堆疊互補式異質場效電晶體組成的反相器電路於不同操作偏壓下,達到(a)低操作偏壓的電壓轉換曲線(Transfer Characteristics),(b)高電壓增益(152V/V),(c)皮瓦(pW)等級的超低靜態功率耗損,(d)高對稱性雜訊邊限特性(~80%)的表現能力。(Source:陽明交大)

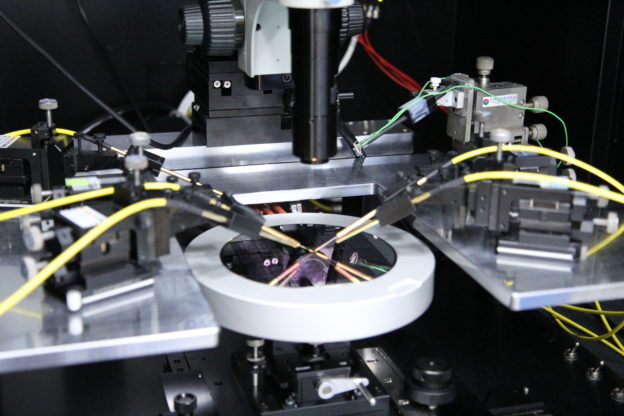

(首圖來源:陽明交大)

延伸閱讀:

標題:目標超越摩爾定律!陽明交大成功挑戰下世代埃米級積體電路技術

地址:https://www.utechfun.com/post/232559.html