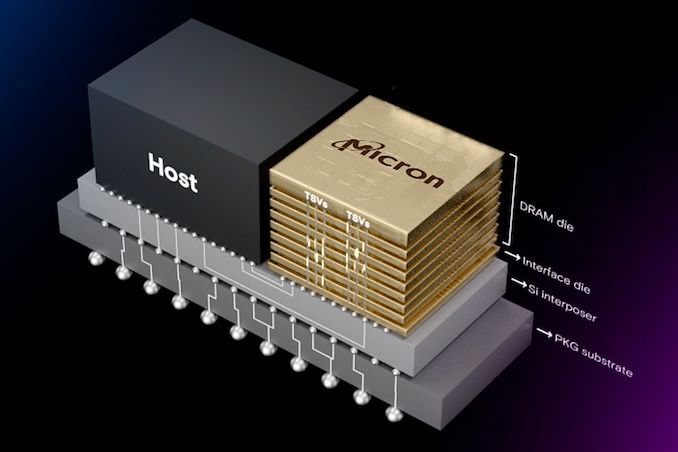

針對當前 AI 市場的需求,預計新一代 HBM4 記憶體將與當前的 HBM 產品有幾項主要的變化,其中最重要的就是記憶體堆疊連結介面標準,將從原本就已經很寬的 1024 位元,進一步轉向倍增到超寬的 2048 位元,這使得 HBM4 記憶體堆疊連結將不再像往常一樣,晶片供應商將需要採用比現在更先進的封裝方法,來容納堆疊連結介面超寬的記憶體。

在日前舉辦的 2024 年歐洲技術研討會上,提供了有關接下來將為 HBM4 製造的基礎晶片一些新細節。未來 HBM4 將使用邏輯製程來生產,由於台積電計劃採用其 N12 和 N5 製程的改良版,藉以完成這項任務。相較於記憶體供應商目前沒有能力可以經濟的生產如此先進的基礎晶片,這一發展預計使得台積電藉此也能在 HBM4 製造中佔據有利地位。

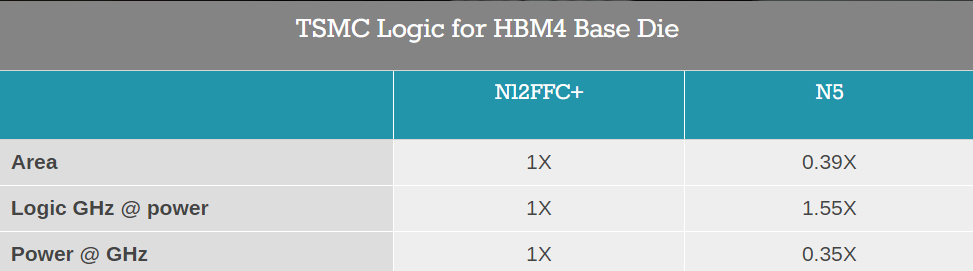

根據 Anandtech 的報導,針對第一波 HBM4 的生產,台積電準備使用兩種製程技術,包括 N12FFC+ 和 N5。根據台積電設計與技術平台高級總監表示,我們正在與主要 HBM 記憶體合作夥伴(美光、三星、SK 海力士)合作,在先進節點上達成 HBM4 的全堆疊整合。其中,在 N12FFC+ 生產的基礎晶片方面是具有成本效益的做法,而 N5 製程技術生產的基礎晶片,則可以在 HBM4 的性能需求下,以更優異的功耗效能提供更多基礎晶片。

報導指出,台積電認為,他們的 12FFC+ 製程非常適合實現 HBM4 效能,使記憶體供應商能夠建構 12 層堆疊 (48 GB) 和 16 層堆疊 (64 GB),每堆疊頻寬超過 2 TB/s。另外,台積電也正在針對 HBM4 透過 CoWoS-L 和 CoWoS-R 先進封裝進行優化,達到 HBM4 的介面超過 2,000 個互連,以達到信號完整性。

另外,N12FFC+ 技術生產的 HBM4 基礎晶片,將有助於使用台積電的 CoWoS-L 或 CoWoS-R 先進封裝技術構建系統級封裝 (SiP),該技術可提供高達 8 倍標線尺寸的中介層,空間足夠容納多達 12 個 HBM4 記憶體堆疊。根據台積電的數據,目前 HBM4 可以在 14mA 電流下達到 6GT/s 的數據傳輸速率。

至於在 N5 製程方面,記憶體製造商也可以選擇採用台積電的 N5 製程來生產 HBM4 基礎晶片。N5 製程建構的基礎晶片將封裝更多的邏輯,消耗更少的功耗,並提供更高的效能。其最重要的好處是這種先進的製程技術可以達到非常小的互連間距,約 6 至 9 微米。這將使得 N5 基礎晶片與直接鍵合結合使用,進而使 HBM4 能夠在邏輯晶片頂部進行 3D 堆疊。直接鍵合可以達到更高的記憶體效能,這對於總是尋求更大記憶體頻寬的 AI 和 HPC 晶片來說預計將是一個巨大的提升。

(首圖來源:台積電)

標題:結合 N12FFC+ 和 N5 製程技術,台積電準備 HBM4 基礎晶片生產

地址:https://www.utechfun.com/post/371817.html