隨著半導體製程不斷微縮,晶圓代工廠加緊腳步開發更先進技術,三大製造商台積電、英特爾和三星都在 IEEE 展示各自開發新電晶體元件 CFET(互補場效應電晶體)的方法。

CFET 可說是 GAAFET 下一代技術,主要使用 3D 堆疊,適合 2 奈米以下製程,不過在介紹最新技術前,我們必須先簡單介紹一下過去的微縮技術,才較好了解這些技術的演變狀況。

半導體(Semiconductor)是導電率介於絕緣體和導體之間的物質或材料,之所以重要,是因為必須控制這個物質或材料導電或不導電。在製程微縮下,要維持這個控制變得越發困難,因此需要進行技術提升,而 MOSFET(金屬氧化物半導體場效電晶體)是目前業界最常使用的場效電晶體(FET),可廣泛用於類比電路與數位電路。

MOSFET:20 奈米以上

知識力科技執行長曲建仲博士先前文章提到,MOSFET 工作原理類似水龍頭的開關,電子由左邊源極(Source)流入,經過閘極(Gate)下方的電子通道,由右邊汲極(Drain)流出,中間的閘極可決定是否讓電子由下方通過。

閘極下方有一層厚度很薄的氧化物(黃色),因為中間由上而下依序為金屬(Metal)、氧化物(Oxide)、半導體(Semiconductor),因此稱為「MOS」。

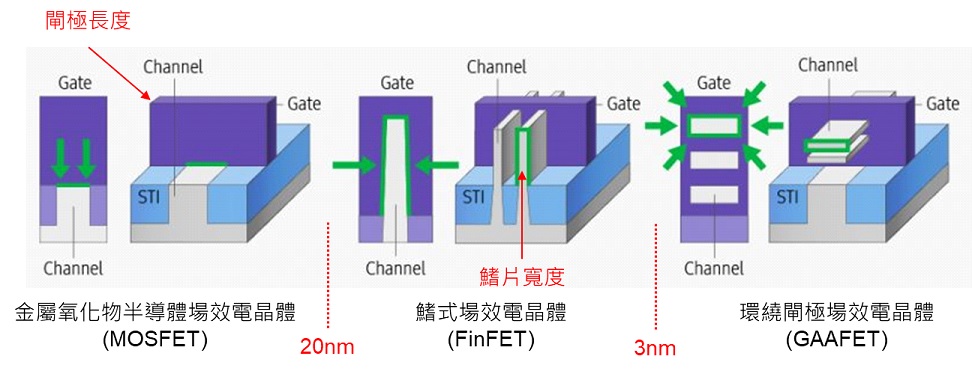

當閘極長度縮小到 20 奈米以下時,電子可能偷溜過去,產生漏電(Leakage)。此外,原本由電壓控制閘極,但當閘極長度越小,與下方通道的接觸面積也越小,因此製程微縮的技術演進目的是「解決漏電」和「增加閘極接觸面積」。

下圖為 MOSFET(適用 20 奈米以上)、FinFET 和 GAAFET(適用 3 奈米以下)技術,可以看出通道的擺放位置開始不同,就是為了增加與閘極(紫色方塊)的接觸面積(綠框處)。

FinFET:16 奈米~3 奈米

當製程縮小至約 16 奈米時,開始改成 FinFET(鰭式場效電晶體),從 2D 平面構造改成 3D 立體結構,並將源極和汲極直立起來(上圖中灰色處),增加與金屬閘極的接觸面積,由於立起來的構造很像魚鰭,因此稱為「鰭式場效電晶體」。

FinFET 能讓電晶體所佔面積變小,且通道三面均被閘極包圍,增加閘極的控制力,減少漏電,不過 3 奈米以下仍遇到物理極限,因此三星提早轉成下一個「環繞閘極電晶體」(Gate-All-Around FET,GAAFET),台積電 3 奈米仍沿用 FinFET 技術。

GAAFET:3 奈米以下

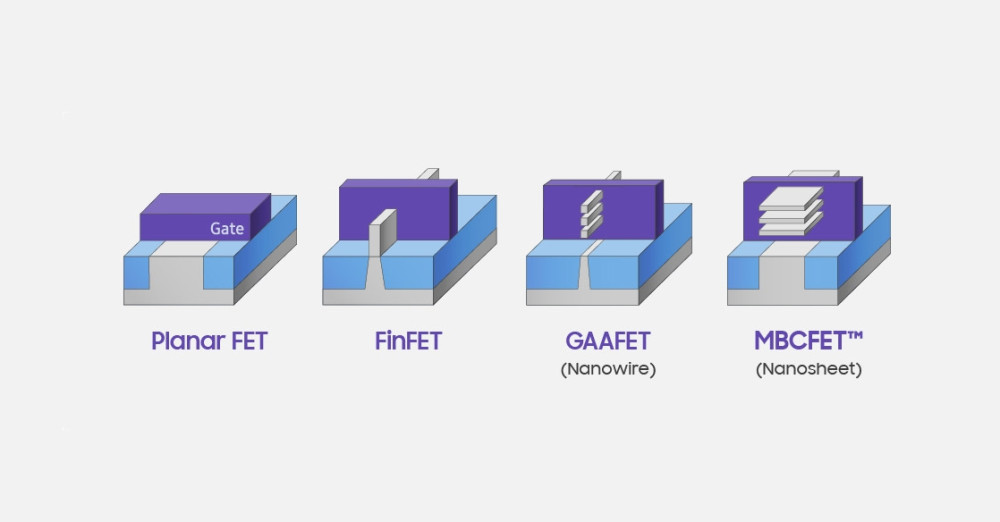

當來到 3 奈米以下時,開始出現漏電問題,因此將鰭式(Fin)從垂直改為水平,開始從 FinFET 轉為「環繞閘極電晶體」(Gate-All-Around FET,GAAFET),來增加更多的接觸面積。其中,三星於 3 奈米提出的 GAAFET 架構稱為「MBCFET」(下圖最右處)。

從圖中可知,GAAFET 和 FinFET 概念類似,只是 GAA 電晶體四個側邊都被閘極包圍,而 FinFET 只有三面。

▲ MBCFET 為三星 3 奈米 GAAFET 架構。(Source:三星)

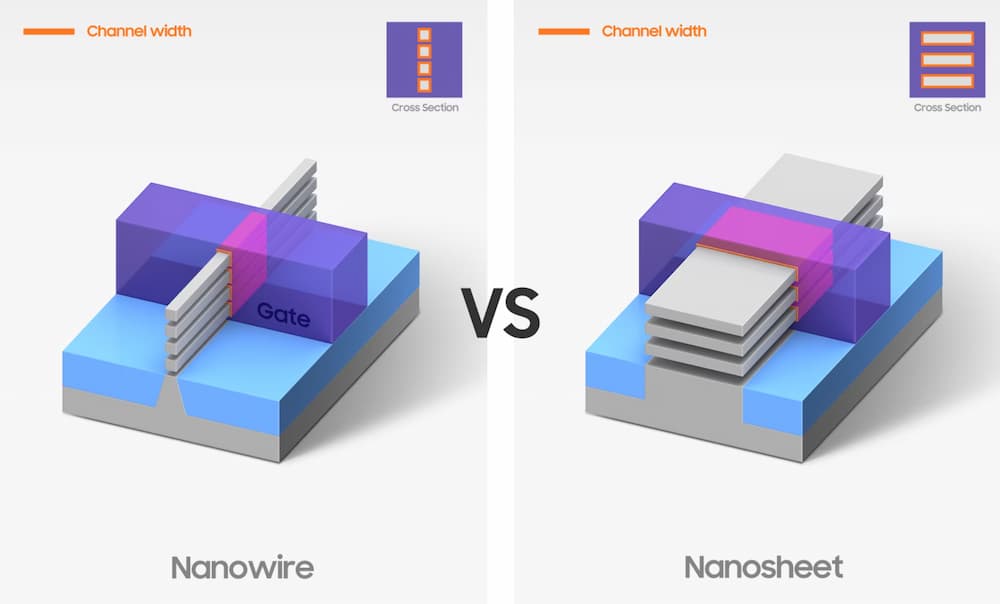

GAAFET 還另外分為奈米片(Nanosheet)和奈米線(Nanowire)結構,前者採用更寬、更薄的鰭片,再使用閘極包覆;後者改為奈米線來增加更多半導體電路,再以閘極包覆。

▲ 左為奈米線,右為奈米片。(Source:)

目前台積電和三星都採用奈米片(Nanosheet)的 GAAFET,三星去年率先公布 3 奈米 GAA MBCFET 技術的最新進展,認為 MBCFET 提供更好的設計靈活性,因為將鰭片橫向堆曡,可自由調整奈米片的高度,並提供比 FinFET 更多的通道寬度選擇。

GAAFET 下一代架構:CFET

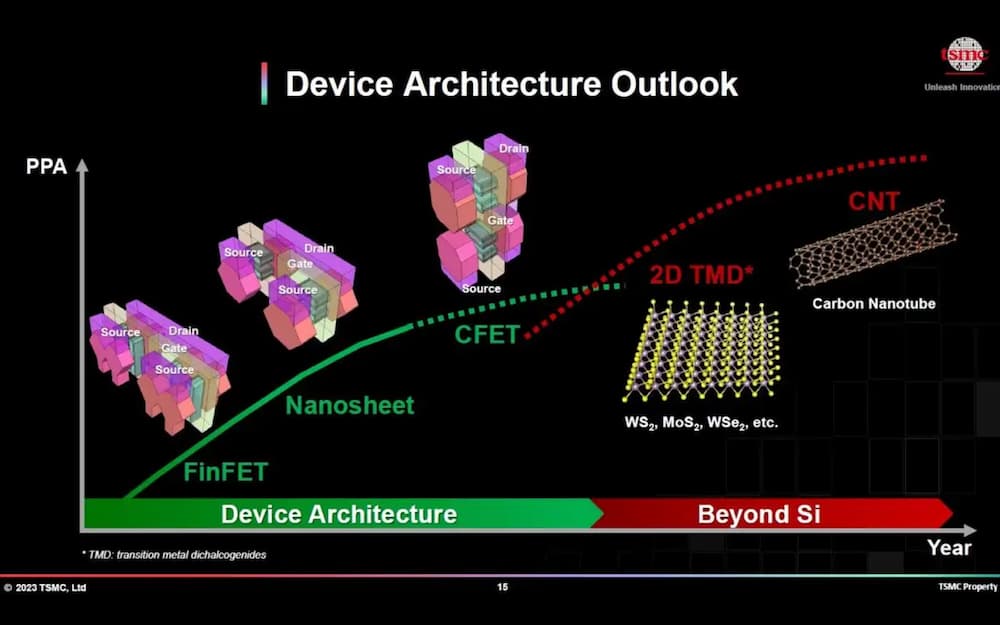

去年台積電在 IEEE 分享的路線圖可知,Nanosheet 之後的下一個技術可能往 CFET、碳奈米管和 2D 材料等低維材料邁進,並表示目前逐步取得突破(即右圖紅線區),有望實現進一步的尺寸和能源微縮。接著,我們先來介紹 CFET 是什麼。

(Source:台積電)

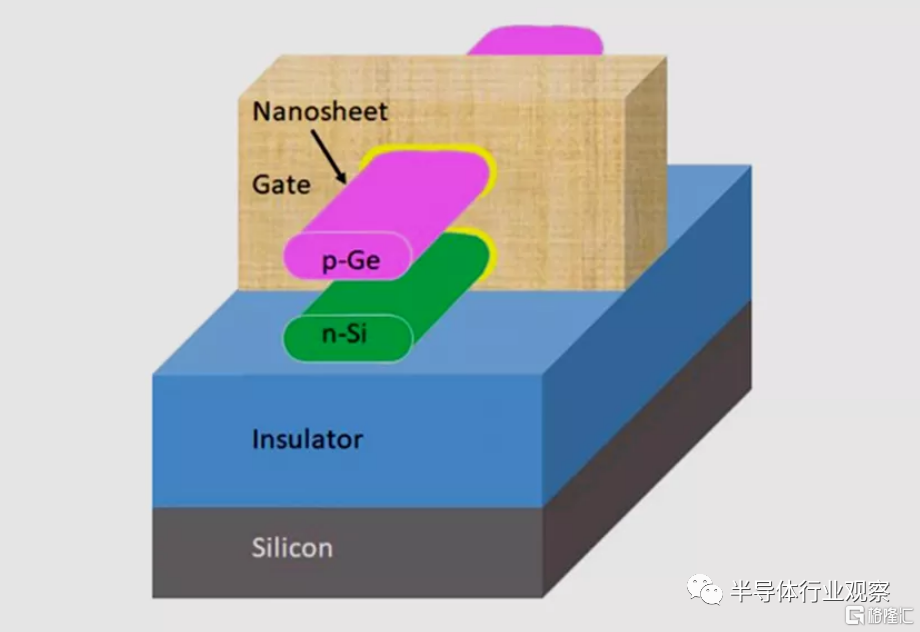

CFET(Complementary FET,互補式場效電晶體 CFET)是將 nMOS和 pMOS 垂直堆疊。這項技術將矽(Si)和鍺(Ge)等不同材料從上下方堆疊,使 p 型和 n 型的場效電晶體更靠近。透過這種疊加方式,CFET 消除 n to p 分開的瓶頸,將運作單元活動區域(cell active area)面積減少 2 倍。

(Source:、半導體產業觀察)

目前業界預計 CFET 技術轉為大規模商用約需 7 至 10 年,目前仍有許多前期準備工作要做。不過外媒報導,根據台積電和英特爾的最新技術展示,CFET 有望成為十年內最可能接替 GAAFET 的下一代先進製程,用於 2 奈米以下技術節點。

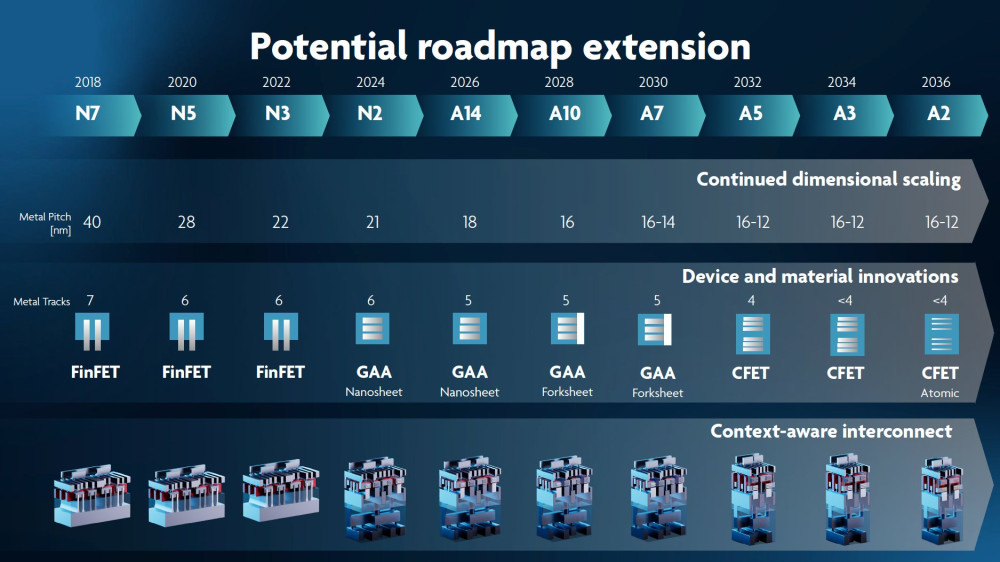

有趣的是,從 imec 分享的潛在技術路線圖(上圖),GAA 架構除了 Nanosheet 外,還有一個叉型片(Forksheet),再來是 CFET,但從去年三家量產狀況來看,製程演進已經稍微放緩,是否如圖中時序進行仍有待商榷。

接著,來看一下英特爾、三星和台積電目前在 CFET 的技術。

英特爾

英特爾去年在 IDEM 展示圍繞 CFET 最簡單電路「逆變器」(inverter),並分享多種改進。英特爾指出,逆變器是在單個鰭片(即單個 CFET)中完成,在最大擴展時,尺寸是目前技術普通 CMOS 逆變器的一半。

英特爾形容,過去晶片技術如同披薩一樣,由下而上層層製造,從電晶體開始,並建立線路層,這包括連接電晶體與金屬層的「訊號互連線」及給電晶體供電的電源線等,最後再進行翻轉和封裝,才成為商用化晶片。

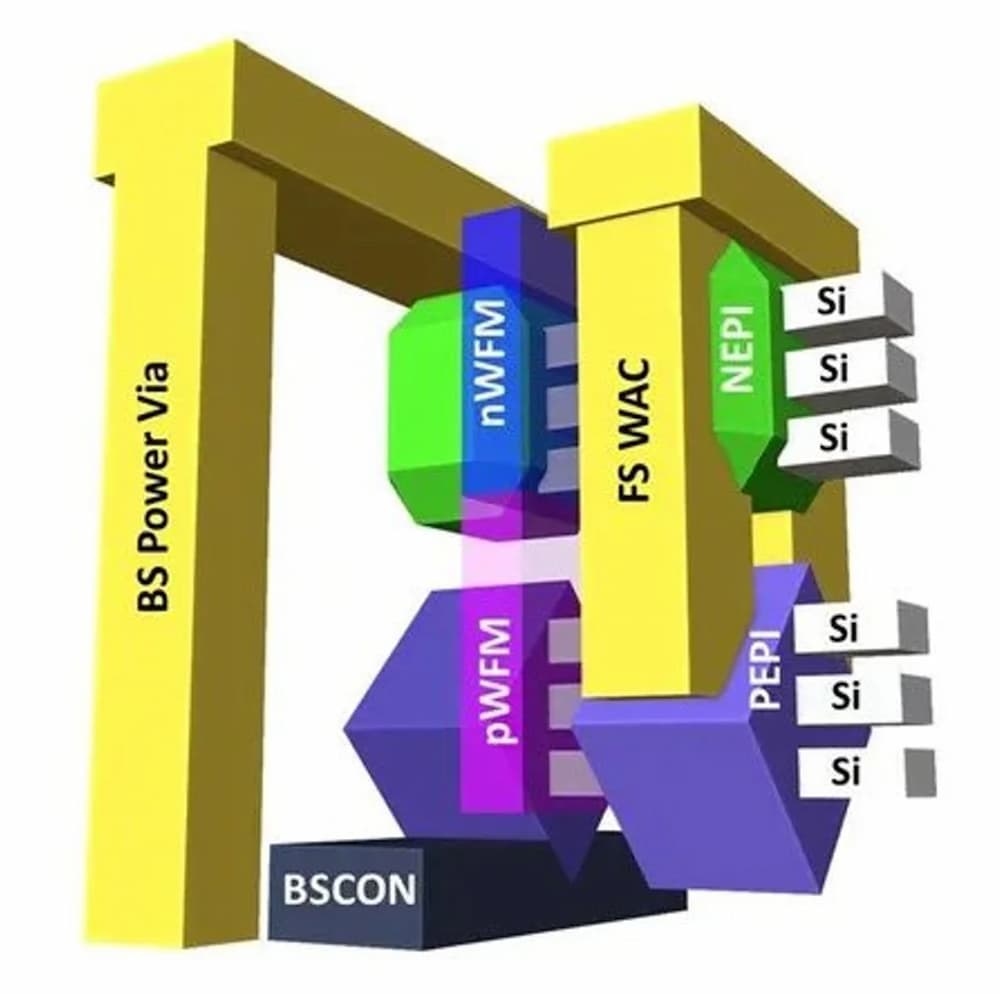

但隨著電晶體縮小,密度變高,線路層架構越來越混亂,堆疊層數越來越多,需要穿過 10 到 20 層堆疊才能為下方的電晶體供電和提供數據訊號。也因此,英特爾研究「晶片背面供電技術」,即所謂的 BSPDN(backside power delivery network),這種新技術能讓互連同時存在矽表面之上和之下。

▲ 英特爾逆變器電路展示圖。(Source:英特爾)

英特爾也展示展示微縮至 60 奈米閘極間距(CPP)的 CFET(或稱 3D 堆疊 CMOS 電晶體),同時結合背面供電和直接背面觸點技術。

三星

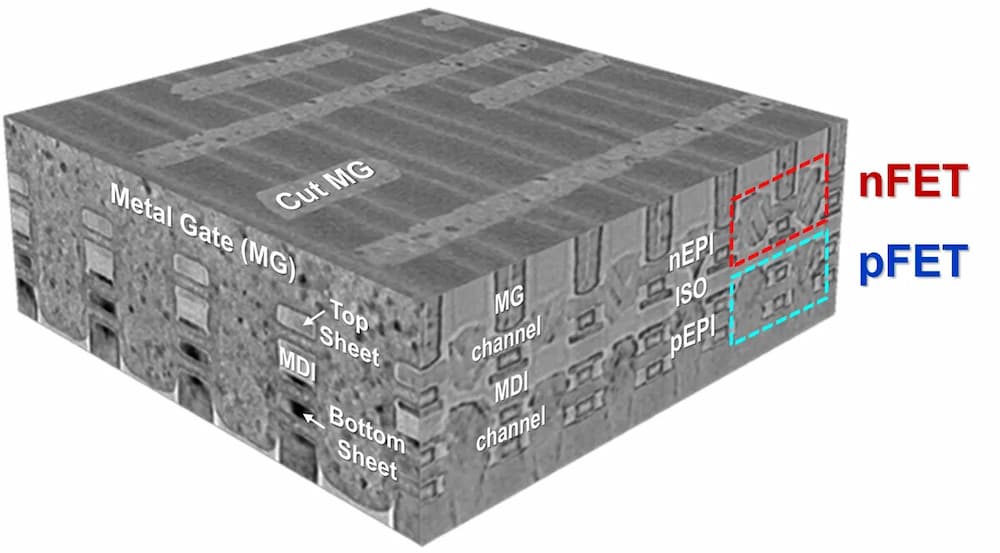

三星將 CFET 稱為「3DSFET 」或 3D 堆疊 FET(3D stacked FET),其展示的 CFET 解決方案,柵極間距為 45 / 48 奈米,比英特爾 60 奈米更小。特別的是,三星嘗試將堆疊 pFET 和 nFET 的源極和汲極進行電氣隔離(electrically isolating),以免電流洩露。

這種隔離方法背後是新型乾式蝕刻技術,取代濕法刻蝕,有助於器件產量提升 80%。與英特爾單個電晶體使用三層奈米片不同,三星是成對電晶體使用單層奈米片。

台積電

台積電也將柵極間距控制在 48 奈米,與三星類似。台積電 CFET 解決方案是在頂部和底部電晶體間形成新介電層,以保持間距。奈米片通常由矽和矽鍺(SiGe)的交替層形成,台積電嘗試矽鍺專用刻蝕法,釋放矽奈米線前於兩個電晶體間構建隔離層。

(Source:台積電)

(首圖來源:shutterstock)

延伸閱讀:

標題:3D 堆疊延續摩爾定律,GAAFET 後下一代 CFET 架構是什麼?任內最後一場法說會,劉德音:過去 30 年台積電經歷,是趟非凡旅程

地址:https://www.utechfun.com/post/320874.html