導讀 近日國外一些大神多位大神對銳龍9000系列進行了詳細的拆解,讓我們得以看到Zen5架構的詳細信息,下面是銳龍9000系列的拆解。 銳龍9000系列採用了經典的chiplet布局,兩顆銳龍都是雙CCD...

近日國外一些大神多位大神對銳龍9000系列進行了詳細的拆解,讓我們得以看到Zen5架構的詳細信息,下面是銳龍9000系列的拆解。

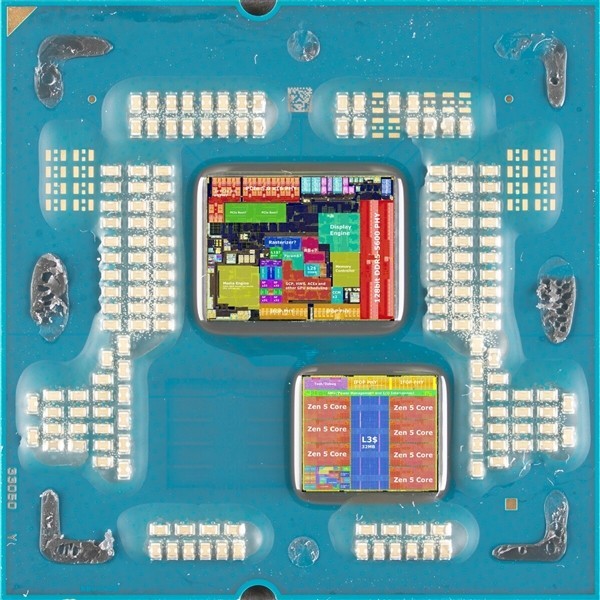

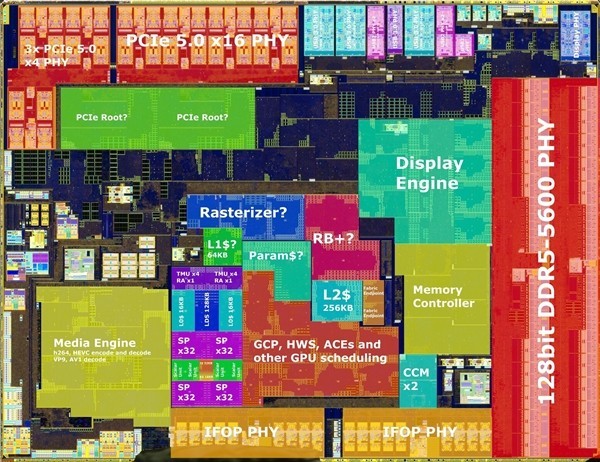

銳龍9000系列採用了經典的chiplet布局,兩顆銳龍都是雙CCD設計,銳龍7和銳龍5則是單CCD,並包含一顆IOD。其中CCD爲N4P 4nm工藝,IOD則是N6 6nm工藝。

布局方面,銳龍9000系列依舊是共享緩存設計,所有核心共享的32MB三級緩存。在架構圖的左下角,有一塊紫色標記的區域,這個部分是專門用於測試和調試的。

可以看到左側佔據了較大面積的部分是矢量執行單元,這部分主要用於執行浮點運算,並且支持完整的512位浮點路徑,兼容AVX-512指令集。由於浮點運算通常會產生較多熱量,因此該單元被設計在核心及整個CCD(Core Complex Die)的邊緣位置,以便於更好地散熱。

轉向右側,我們會發現這裏是二級緩存的位置,它緊密連接着三級緩存,以加速數據訪問速度。

而位於中心的部分則包含了處理器前端的核心組件,如指令預取與解碼邏輯、分支預測機制、微操作緩存和調度器等。此外,這裏還集成了32KB的一級指令緩存、48KB的一級數據緩存、整數執行單元以及負責內存讀寫的載入/存儲單元。這一系列組件共同構成了處理器處理指令流的關鍵路徑,對提升整體性能至關重要。

標題:國外大神拆解銳龍9000系列 Zen5架構細節露出

地址:https://www.utechfun.com/post/429173.html