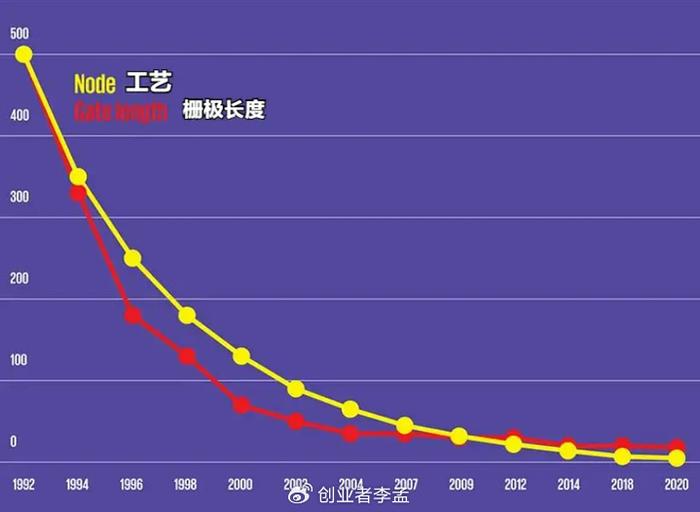

如何評價網傳 ASML「掀老底」稱 3nm 芯片實際爲 23nm,1nm 芯片是 18nm?近日,ASML在公布自己的EUV光刻機路线圖時,更是將各大晶圓廠的老底掀开了,ASML的PPT,非常清楚的指出了各大晶圓工藝,對應的金屬半節距,如果按照最开始芯片工藝的說法,這個才是實際的芯片工藝。如上圖所示,N3(3nm工藝)對應的是23nm,N2(2nm工藝)對應的是22nm,A14(1.4nm工藝)對應的是21nm。A10也就是1nm時,對應的是18nm,A7也就是0.7nm時,應對的是18-16nm,甚至到A2,也就是0.2nm時,實際金屬半間距是16-12nm。

在評價這個問題之前,我們需要了解一下背景知識。半導體工藝節點的命名,如7nm、5nm、3nm等,並不直接對應實際的物理尺寸,而是行業內約定俗成的一種命名方式。這些數字大致反映了晶體管的密度和性能水平,但並不是嚴格的幾何度量。隨着工藝技術的進步,這種命名與實際物理尺寸之間的差異變得越來越大。

ASML作爲全球領先的光刻機制造商,其公布的EUV光刻機路线圖和晶圓工藝數據具有很高的參考價值。這些數據揭示了實際芯片工藝與宣傳工藝之間的差距,對於了解半導體行業的真實情況具有重要意義。ASML的曝光事件對全球芯片行業產生了顯著影響,特別是對於那些依賴ASML先進光刻機的公司。

根據ASML的PPT,我們來復盤總結下關鍵數據:

- N3(3nm工藝)實際對應的金屬半節距爲23nm。

- N2(2nm工藝)實際對應的金屬半節距爲22nm。

- A14(1.4nm工藝)實際對應的金屬半節距爲21nm。

- A10(1nm工藝)實際對應的金屬半節距爲18nm。

- A7(0.7nm工藝)實際對應的金屬半節距爲18-16nm。

- A2(0.2nm工藝)實際對應的金屬半節距爲16-12nm。

從這些數據中,我們可以得出以下幾點結論:

1、實際芯片工藝與宣傳工藝之間存在差距。這可能是因爲宣傳工藝是基於晶體管的物理尺寸,而實際工藝受到多種因素的影響,如光刻機的分辨率、材料的性質等。

2、隨着工藝的進步,實際工藝與宣傳工藝之間的差距逐漸縮小。這表明隨着技術的發展,半導體行業正在逐步克服各種技術難題,提高芯片的制造精度。隨着技術的發展,實現更小制程的技術難度呈指數級增長。爲了繼續推進摩爾定律,工程師們不得不採用越來越復雜的設計和制造技術,這導致了實際物理尺寸與工藝節點名稱之間的差距。

3、盡管存在差距,但半導體行業仍在不斷努力推動工藝的發展。從3nm到1nm,再到0.7nm和0.2nm,每一次工藝的進步都代表着人類對微觀世界的探索又向前邁進了一步。

4、工藝節點命名的抽象性,我們發現工藝節點的名稱更多是一個市場營銷術語,而不是精確的科學度量。這種命名方式有助於消費者理解不同代技術的相對進步,但也可能導致誤解。

5、行業透明度,ASML公开這樣的信息可能是爲了提高行業透明度,讓客戶和市場更加清晰地了解不同工藝節點的實際技術水平。這也可能有助於調整市場對先進工藝的期望。

6、對競爭的影響,這種信息的公开可能會影響不同半導體制造商之間的競爭,因爲它揭示了誰真正領先於技術創新和誰可能在營銷上過於誇大其詞。

總結整理後,我們會發現,ASML公布的這些數據揭示了半導體行業的真實情況,雖然實際工藝與宣傳工藝之間存在差距,但這並不妨礙行業內的技術進步和發展。對此大家是怎么看的,歡迎關注我創業者李孟和我一起交流!

標題:ASML“掀老底”,稱3nm芯片實際爲23nm,我們竟被芯片企業營銷了

地址:https://www.utechfun.com/post/387210.html