近期光刻機龍頭ASML突然發瘋,發布PPT,揭开了台積電的等芯片制造企業的先進工藝的技術細節,指出台積電等的先進工藝,其實從28納米以後就已脫離了原來的芯片工藝命名規則,芯片工藝的命名早已脫離了原來的命名規則。

ASML指出在28納米以上工藝的時候,芯片制造工藝的柵極間距都低於芯片工藝的名字,即是65納米,芯片的柵極間距低於65納米,但是在28納米以下工藝,芯片的柵極間距難以迅速縮短,芯片制造企業的命名已是脫離了這樣的命名規則。

ASML表示3納米工藝的柵極間距爲23納米,2納米、1.4納米工藝的柵極間距分別爲22納米、21納米,預計1納米的柵極間距爲18納米,甚至芯片制造企業可以根據這樣的命名方式突破1納米,0.2納米工藝對應的柵極間距爲12納米左右。

專家就指出當下的硅基芯片極限工藝是1納米,因爲1納米僅相當於2-3個硅原子的厚度,那樣硅芯片可能會極爲不穩定,電子容易擊穿柵極,然而按照這種等效工藝命名規則,卻可以出現出現0.1納米的芯片制造工藝。

台積電的芯片工藝命名其實早在10納米的時候就已被質疑,當時台積電研發出10納米工藝的時候,高通就在內部指出10納米工藝的性能提升有限,估計僅是與Intel的14納米工藝相當,認爲台積電誇大了10納米工藝的性能,而後來10納米工藝也是迅速被舍棄。

芯片工藝的命名規則發生改變,主要是由台積電和三星改變的,這兩家芯片制造工藝認爲自己的14/16納米工藝上已追上了Intel,然而實際上他們的14/16納米工藝其實比Intel的14納米落後,三星的14納米尤爲落後,當時用三星的14納米工藝生產的A9處理器就出現發熱問題,而台積電的16納米工藝生產的A9處理器性能更強、功耗更低。

但是台積電和三星此後不斷升級工藝,芯片工藝性能相比自己的原有工藝提升20%-30%,已可以稱爲一代新工藝,同時如此也可以聲稱趕超Intel,再加上這兩家芯片代工企業代表着最先進的水平,同時更先進的工藝又可以幫助芯片企業進行營銷,於是各方就默認了台積電和三星的命名規則,當然到了後來的5納米工藝之後,台積電和三星在芯片制造工藝方面確實超越了Intel。

如今ASML突然翻出這回事,並對業界大肆宣傳,也並非沒有私心,此舉或是爲了給它研發下一代的光刻機進行營銷造勢。此前ASML曾宣稱2納米EUV光刻機將是最後一代光刻機,不過如今日本、美國在EUV光源方面已取得了一定的突破。

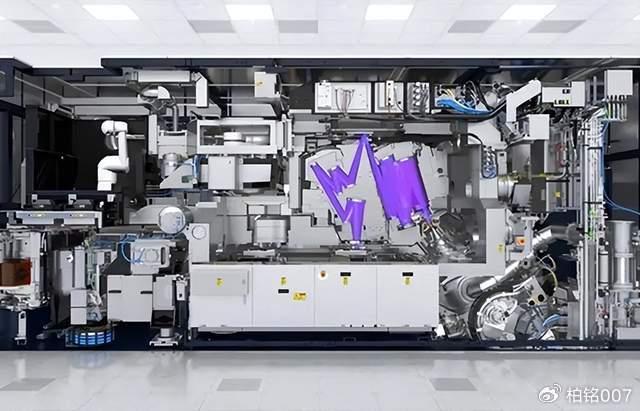

當前的2納米EUV光刻機的EUV光纖爲13.5納米波長,這樣的波長也說明當下的2納米EUV光刻機生產的芯片柵極長度必然大於13.5納米;日本和美國研發的新光源被命名爲EUV-FEL,產生的光线波長將縮減到6.6-6.7納米,可以進一步縮減芯片的柵極長度。

日本尼康、佳能和荷蘭的ASML爲全球僅剩的3家光刻機生產企業,日本希望重振光刻機產業,荷蘭ASML則和美國深度捆綁,先進的EUV-FEL將引發日本和荷蘭爭奪光刻機產業,如此就可以延續他們的光刻機事業。

光刻機是一項很賺錢的生意,DUV光刻機只要數千萬美元,第一代EUV光刻機售價1.2億美元,2納米EUV光刻機售價高達3.8萬億美元,這個市場如今就由佳能、尼康和ASML三家佔有,誰先研發成功EUV-FEL,那么誰將成爲下一代EUV光刻機的霸主,這也是ASML如此不顧台積電和三星的情面,而揭开芯片工藝真相的原因吧。

標題:ASML掀开台積電的老底,28納米以後的芯片工藝升級都是假的!

地址:https://www.utechfun.com/post/385155.html