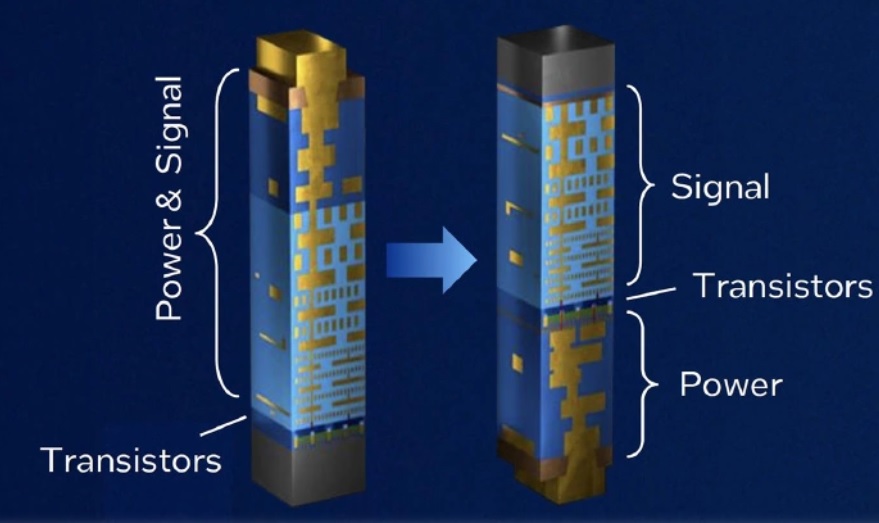

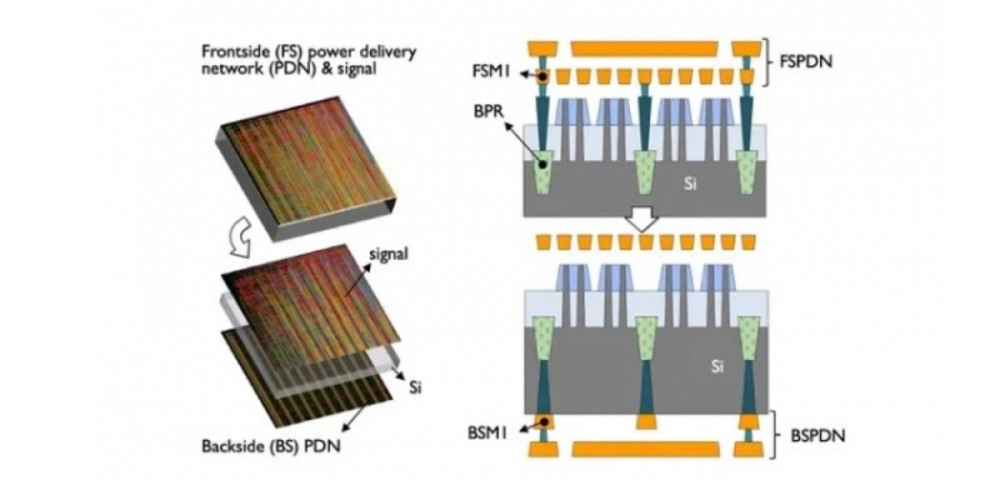

隨著摩爾定律的演進,電晶體越來越小,密度越來越高,堆疊層數也越來越多,可能需要穿過 10~20 層堆疊才能為下方電晶體提供電源和數據訊號,這導致互連線和電源線共存的線路層變成了一個越來越混亂的網路。同時,電子在向下傳輸的過程中,會出現 IR 壓降現象,導致電力損失產生。

除了電力損失,供電線路佔用空間也是問題。晶片電源線路佈線複雜的後段製程,往往佔至少 20% 資源,如何解決訊號網路跟供電網路資源排擠問題,使元件微縮,變成晶片設計者主要挑戰,這就造成半導體業界開始把供電網路轉移到晶片背面的原因。

台積電超級電軌 2025 年 A16 製程上亮相,技術複雜提高晶片效率

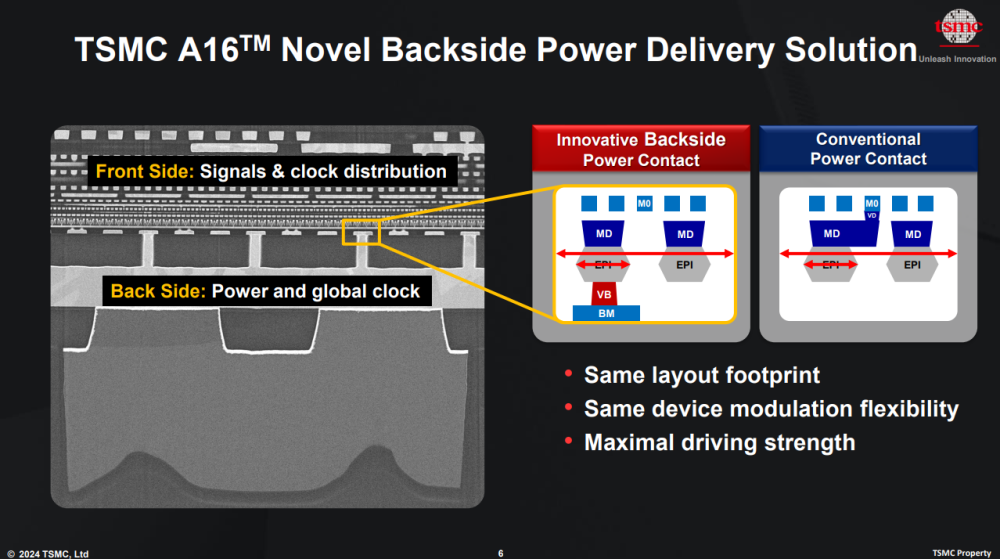

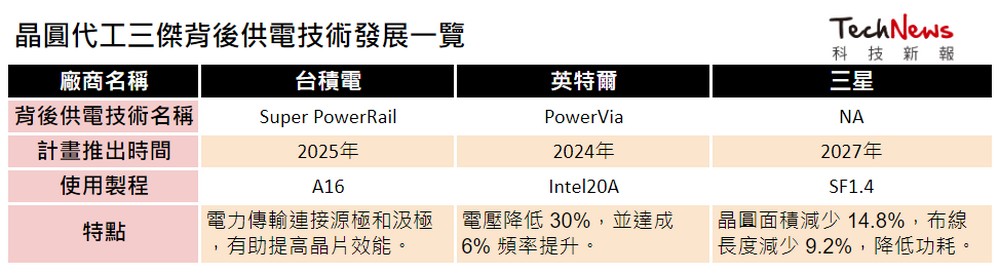

晶圓代工龍頭日前在北美技術論壇發表 A16 節點製程,除了容納更多電晶體,提升運算效能,更降低能耗。更令人關切的,在 A16 晶片導入結合超級電軌 (Super PowerRail) 架構與奈米片電晶體,帶動運算速度更快、更有效率的資料中心處理器發展。尤其,台積電 A16 採不同晶片佈線。向電晶體輸送電力的電線將位於電晶體下方而不是上方,稱為背面供電,有利生產更有效率的晶片。

事實上,最佳化處理器的方法之一是緩解 IR 壓降,這現象會降低晶片電晶體接收的電壓,降低性能。A16 電線不太容易出現電壓下降、不僅簡化電力分配,還允許晶片電路更緊密封裝,目標是處理器放入更多電晶體以提高運算能力。而且,電晶體由四個主要元件組成,源極、汲極、通道和閘極。源極是電流流入電晶體的入口點,汲極是出口,通道和閘極依序負責協調電子的運動。

台積電在 A16 製程技術上將電力傳輸線直接連接源極和汲極。對此,台積電表示,決定更複雜設計是因有助提高晶片效能。在此情況下,使用超級電軌的 A16 將較 N2P 相同 Vdd (工作電壓) 下,運算速度增加 8%~10%,或相同運算速度下,功耗降低 15%~20%,晶片密度提升高達 1.10 倍,支援資料中心產品。

英特爾 PowerVia 將在 2024 年於 Intel 20A 上生產就緒

與台積電超級電軌相同的,英特爾也推出背後供電解決方案 PowerVia。據介紹,電源線原本可能佔據晶片上面 20% 的空間,但 PowerVia 背後供電技術節省了這一空間,也意味著互連層可以變得更寬鬆一些。

對此,先前英特爾團隊還特地製作 Blue Sky Creek 測試晶片證明,背後供電技術電源線和互連線可分離並線徑更大,以改善供電和訊號傳輸。測試結果顯示,晶片大部分區域的標準單元利用率都超過 90%,平台電壓降低 30%,並達成 6% 頻率提升,同時單元密度也大幅增加,並有望降低成本。PowerVia 測試晶片也展示良好的散熱特性,符合邏輯微縮預期將實現的更高功率密度。

另外,PowerVia 也計劃導入到英特爾代工服務(IFS)當中,使客戶所設計的晶片能更快地達到產品能效和性能的提升。根據英特爾 PowerVia 背後供電技術的官方介紹,英特爾將在 Intel 20A 製程技術上採用 PowerVia 背後供電技術及 RibbonFET 全環繞柵極電晶體的架構,預計 2024 上半年生產準備就緒,用於未來量產客戶端 ARL 平台,正在晶圓廠啟動步進(First Stepping)。

三星計劃 2027 年開始在 SF1.4 製程上應用

至於,台積電另一競爭對手三星除了率先轉型 GAA 電晶體技術之外,其背後供電技術(BSPDN)也是三星追逐先進製程的殺手鐧。根據先前南韓媒體報導,三星代工部門技術長 Jung Ki-tae Jung 曾宣布,2027 年將背後供電技術用於 1.4 奈米製程。

報導指出,與傳統前端供電網路相比,三星的背後供電網路成功將耗用晶圓面積減少 14.8%,晶片擁有更多空間,可增加更多晶體管,提高整體性能,佈線長度減少 9.2%,有助降低電阻使更多電流通過,降低功耗,改善功率傳輸狀況。三星電子相關人士表示,採用背後供電技術的半導體的量產時間,可能會根據客戶的時程安排而有所不同。三星正在調查背後供電技術應用的客戶需求。

(首圖來源:科技新報攝)

標題:台積電、英特爾、三星背後供電技術比一比,力拚先進製程市場

地址:https://www.utechfun.com/post/367887.html